Extension Instruction Specifications

3-14

MULQIU (Unsigned high-speed multiplication instruction: between immediate value and register)

[Instruction Format (Macro Name)]

MULQIU imm, Dn

[Assembler Mnemonic]

udfu01 imm8, Dn :imm8 is zero-extended

udfu01 imm16, Dn :imm16 is zero-extended

udfu01 imm32, Dn

[Operation]

This instruction performs multiplication quickly using the multiplier of the extension function unit.

The 32-bit data obtained by zero-extending imm (multiplicand) and the contents of Dn (unsigned 32-bit integer:

multiplier) are multiplied, and the upper 32 bits of the results (64 bits) are written into the high-speed multiply

register MDRQ and the lower 32 bits into Dn.

The significant value range of the multiplicand stored in imm before the operation is judged (starting point: LSB,

judgment unit: 2 bytes), and the operation is only performed for the range containing these significant values. In

other words, if the number of imm bits is “16” or less, the operation results will be derived faster.

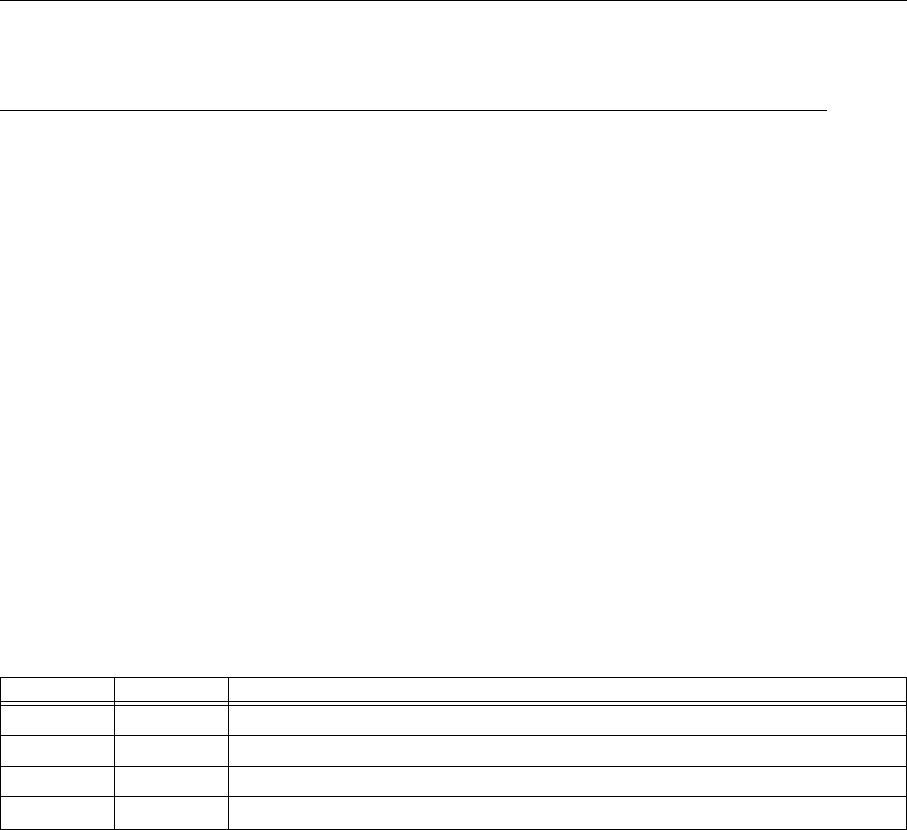

[Flag Changes]

Flag Change Condition

V * Undefined

C * Undefined

N + 1 when MSB of the lower 32 bits of the results is 1; 0 in all other cases

Z + 1 when the lower 32 bits of results are 0; 0 in all other cases

[Programming Cautions]

PSW updating by flag changes is delayed by one instruction.

However, Bcc and Lcc instructions can evaluate flags without waiting for flag reflection to PSW.