293

CHAPTER 16 SERIAL INTERFACE CHANNEL 0 (

µ

PD78058F SUBSERIES)

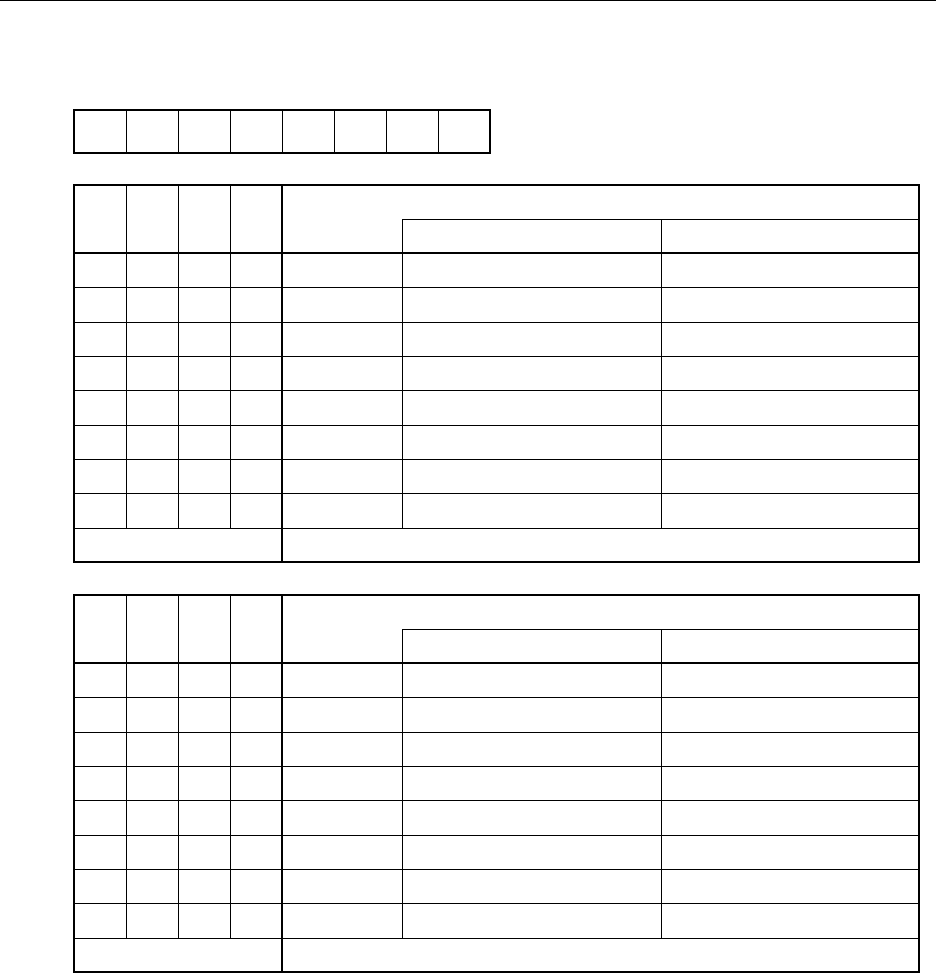

Serial Interface Channel 0 Serial Clock Selection

TCL33 TCL32 TCL31 TCL30

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

0

1

0

1

0

1

0

1

f

XX/2

f

XX/2

2

fXX/2

3

fXX/2

4

fXX/2

5

fXX/2

6

fXX/2

7

fXX/2

8

Setting prohibited

f

X/2

2

(1.25 MHz)

f

X/2

3

(625 kHz)

f

X/2

4

(313 kHz)

f

X/2

5

(156 kHz)

f

X/2

6

(78.1 kHz)

f

X/2

7

(39.1 kHz)

f

X/2

8

(19.5 kHz)

f

X/2

2

(1.25 MHz)

f

X/2

3

(625 kHz)

f

X/2

4

(313 kHz)

f

X/2

5

(156 kHz)

f

X/2

6

(78.1 kHz)

f

X/2

7

(39.1 kHz)

f

X/2

8

(19.5 kHz)

f

X/2

9

(9.8 kHz)

Other than above Setting prohibited

Serial Interface Channel 1 Serial Clock Selection

TCL37 TCL36 TCL35 TCL34

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

0

1

0

1

0

1

0

1

f

XX/2

f

XX/2

2

fXX/2

3

fXX/2

4

fXX/2

5

fXX/2

6

fXX/2

7

fXX/2

8

Setting prohibited

f

X/2

2

(1.25 MHz)

f

X/2

3

(625 kHz)

f

X/2

4

(313 kHz)

f

X/2

5

(156 kHz)

f

X/2

6

(78.1 kHz)

f

X/2

7

(39.1 kHz)

f

X/2

8

(19.5 kHz)

f

X/2

2

(1.25 MHz)

f

X/2

3

(625 kHz)

f

X/2

4

(313 kHz)

f

X/2

5

(156 kHz)

f

X/2

6

(78.1 kHz)

f

X/2

7

(39.1 kHz)

f

X/2

8

(19.5 kHz)

f

X/2

9

(9.8 kHz)

Other than above Setting prohibited

65432107

Symbol

TCL3 TCL37 TCL36 TCL35 TCL34 TCL33 TCL32 TCL31 TCL30

FF43H 88H R/W

Address After Reset R/W

MCS = 1 MCS = 0

MCS = 1 MCS = 0

Figure 16-3. Timer Clock Select Register 3 Format

Caution When rewriting TCL3 to other data, stop the serial transfer operation beforehand.

Remarks 1. fXX : Main system clock frequency (fX or fX/2)

2. fX : Main system clock oscillation frequency

3. MCS : Bit 0 of oscillation mode selection register (OSMS)

4. Figures in parentheses apply to operation with f

X = 5.0 MHz.