56

CHAPTER 2 OUTLINE (

µ

PD78058FY SUBSERIES)

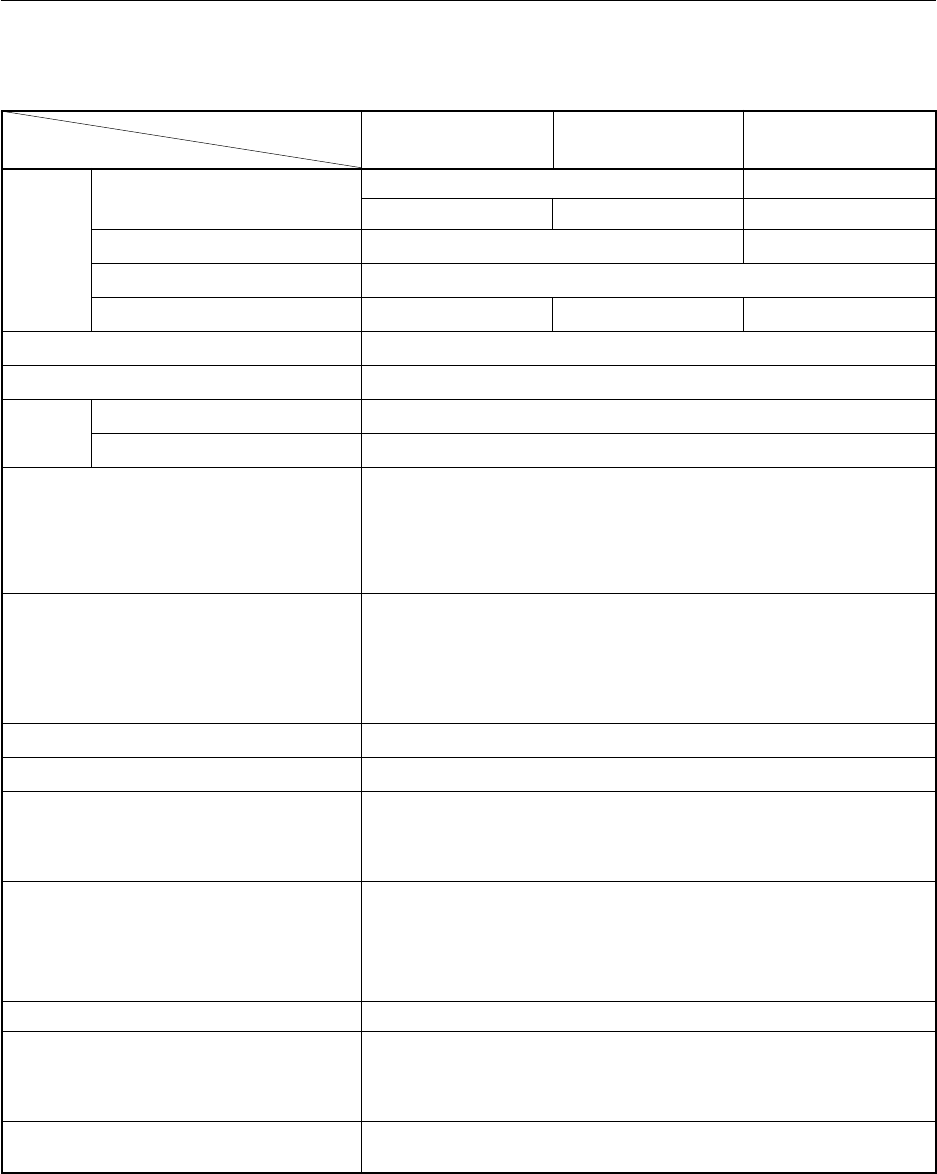

2.8 Outline of Function

ROM Mask ROM PROM

48 Kbytes 60 Kbytes 60 Kbytes

Note 1

High-speed RAM 1024 bytes 1024 bytes

Note 1

Buffer RAM 32 bytes

Expansion RAM None 1024 bytes 1024 bytes

Note 2

Memory space 64 Kbytes

General register 8 bits × 8 × 4 banks

With main system clock selected 0.4

µ

s/0.8

µ

s/1.6

µ

s/3.2

µ

s/6.4

µ

s/12.8

µ

s (at 5.0-MHz operation)

With subsystem clock selected 122

µ

s (at 32.768-kHz operation)

Instruction set • 16-bit operation

• Multiply/divide (8 bits × 8 bits, 16 bits ÷ 8 bits)

• Bit manipulate (set, reset, test, and Boolean operation)

• BCD adjust, etc.

I/O port • Total : 69

• CMOS input : 2

• CMOS I/O : 63

• N-ch open-drain I/O : 4

A/D converter 8-bit resolution × 8 channels

D/A converter 8-bit resolution × 2 channels

Serial interface

• 3-wire serial I/O/2-wire serial I/O/I

2

C bus mode selection possible : 1 channel

• 3-wire serial I/O mode (Max. 32-byte on-chip auto-transmit/receive) : 1 channel

• 3-wire serial I/O/UART mode selectable : 1 channel

Timer • 16-bit timer/event counter : 1 channel

• 8-bit timer/event counter : 2 channels

• Watch timer : 1 channel

• Watchdog timer : 1 channel

Timer output Three outputs: (14-bit PWM output enable: 1)

Clock output 19.5 kHz, 39.1 kHz, 78.1 kHz, 156 kHz, 313 kHz, 625 kHz, 1.25 MHz,

2.5 MHz, 5.0 MHz (at 5.0-MHz operation with main system clock)

32.768 kHz (at 32.768-kHz operation with subsystem clock)

Buzzer output 1.2 kHz, 2.4 kHz, 4.9 kHz, 9.8 kHz (at 5.0-MHz operation with main system

clock)

Notes 1. The capacities of the internal PROM and the internal high-speed RAM can be changed using the

memory switching register (IMS).

2. The capacity of the internal expansion RAM can be changed using the internal expansion RAM size

switching register (IXS).

µ

PD78056FY

µ

PD78058FY

µ

PD78P058FY

Item

Part Number

Minimum

instruction

execution

time

Internal

memory