419

CHAPTER 18 SERIAL INTERFACE CHANNEL 1

(c) Repeat transmission mode

In this mode, data stored in the internal buffer RAM is transmitted repeatedly.

Serial transmission is started by writing the desired data to serial I/O shift register 1 (SIO1) when bit 7

(CSIE1) of serial operation mode register 1 (CSIM1) is set at 1.

Unlike the case of the basic transmission mode, an interrupt request flag (CSIIF1) is not set after sending

the final byte (FAC0H address data), but the auto data send and receive address pointer (ADTP) is reset

to the value it was at when transmission was started and the contents of the internal buffer’s RAM are

resent.

When a reception operation, busy control and strobe control are not performed, the P20/SI1, P23/STB

and P24/BUSY pins can be used as ordinary input/output ports.

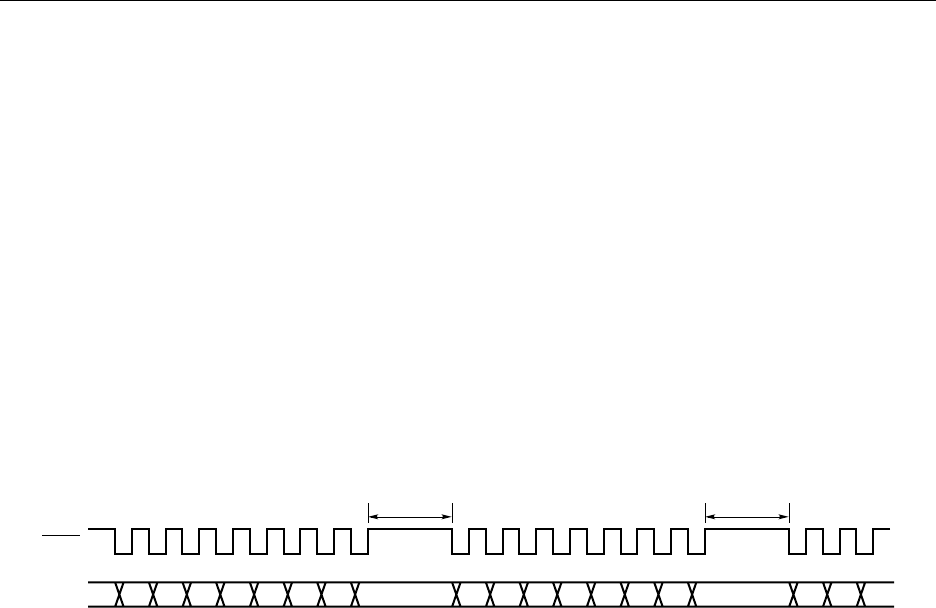

The repeat transmission mode operation timing is shown in Figure 18-14, and the operation flowchart in

Figure 18-15. Figure 18-16 shows the operation of the internal buffer RAM when 6 bytes of data are

transmitted in the repeat transmission mode.

Figure 18-14. Repeat Transmission Mode Operation Timing

D7 D6 D5 D4 D3 D2 D1 D0 D7 D6 D5 D4 D3 D2 D1 D0

Interval Interval

D7 D6 D5

SCK1

SO1

Caution Since, in the repeat transmission mode, a read is performed on the internal buffer RAM

after the transmission of one byte, the interval is included in the period up to the next

transmission. As the internal buffer RAM read is performed at the same time as CPU

processing, the maximum interval is dependent upon the CPU operation and the value

of the automatic data transmit/receive interval specify register (ADTI) (see (5) "Auto-

matic transmit/receive interval time").