591

APPENDIX E REVISION HISTORY

Major revisions by edition and revised chapters are shown below.

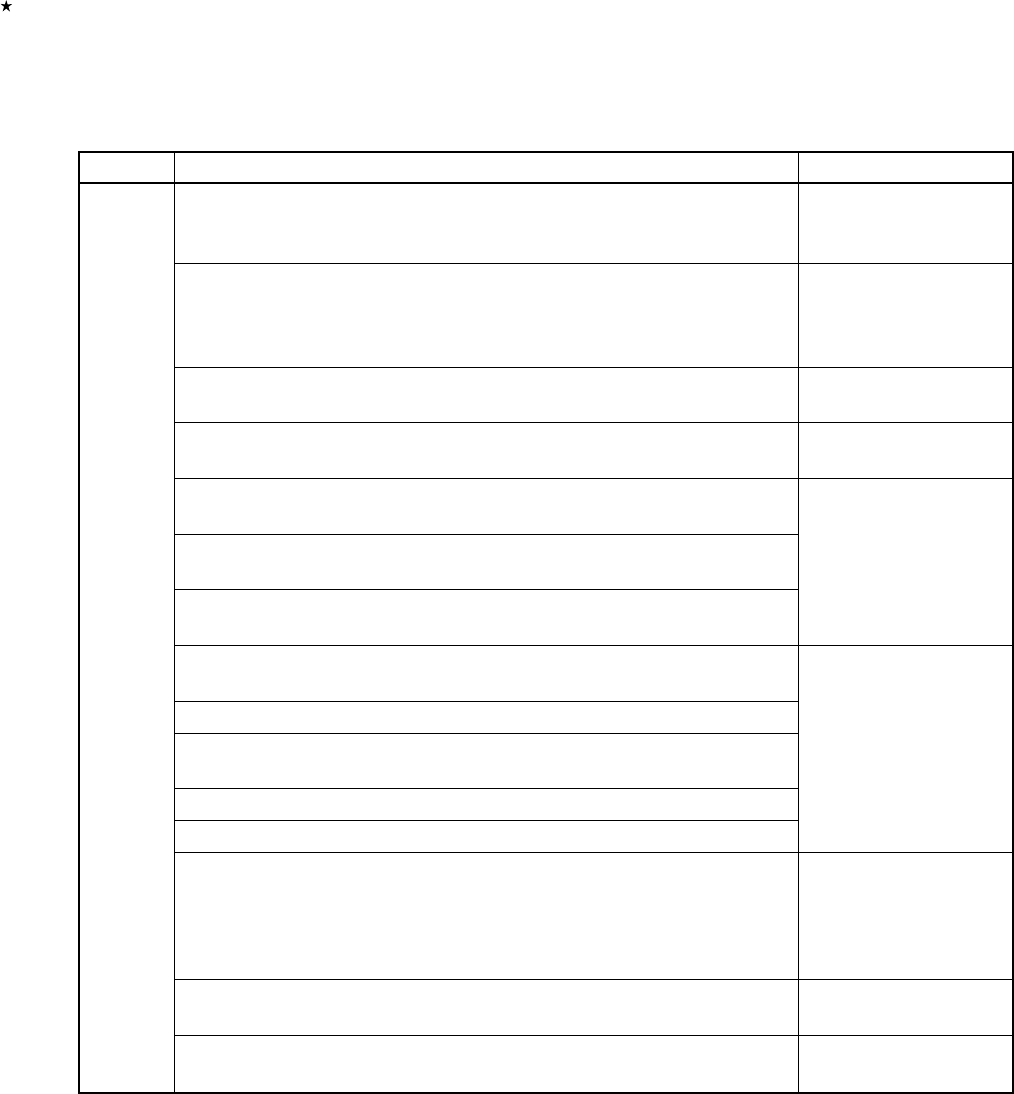

Edition Major Revisions from Previous Edition Revised Chapters

2nd The following products have already been developed: Throughout

µ

PD78056GC-×××-8BT, 78058FGC-×××-8BT, 78P058FGC-8BT,

78056FYGC-×××-8BT, 78058FYGC-×××-88BT

The block diagrams of the following ports were changed. CHAPTER 6 PORT

Figures 6-5 and 6-7 P20, P21, P23 to P26 Block Diagram, Figures 6-6 and FUNCTIONS

6-8 P22 and P27 Block Diagram, Figure 6-9 P30 to P37 Block Diagram,

Figure 6-16 P71 and P72 Block Diagram

Table 7-2 Relationship between CPU Clock and Minimum Instruction CHAPTER 7 CLOCK

Execution Time was added. GENERATOR

Figures 9-10 and 9-13 Square-Wave Output Operation Timing were added. CHAPTER 9 8-BIT

TIME/EVENT COUNTER

Note related to operation control in the SBI mode for serial interface channel 0 CHAPTER 16 SERIAL

was added. INTERFACE CHANNEL 0

Note related to BSYE in Figure 16-5 Serial Bus Interface Control Register

(

µ

PD78058F SUBSERIES)

Format was changed.

Cautions were added to 16.4.3 (2) (a) Bus release signal (REL) and (b)

Command signal (CMD)

CSCK was deleted from Figure 19-1 Serial Interface Channel 2 Block Diagram CHAPTER 19 SERIAL

and Figure 19-2 Baud Rate Generator Block Diagram INTERFACE CHANNEL 2

Figure 19-3 Serial Operating Mode Register 2 Format was changed.

Table 19-2 Serial Interface Channel 2 Operating Mode Settings (2) 3-Wire

serial I/O mode was changed.

Figure 19-10 Receive Error Timing was changed.

19.4.4 Restrictions on using UART mode was added.

APPENDIX A. DIFFERENCES AMONG THE

µ

PD78054, 78058F, AND 780058 APPENDIX A

SUBSERIES was added. DIFFERENCES

AMONG

µ

PD78054,

78058F, AND 780058

SUBSERIES

Overall revision: Contents were adapted to correspond with in-circuit emulators APPENDIX B

IE-78K0-NS and IE-78001-R-A DEVELOPMENT TOOLS

Overall revision: Fuzzy inference development support system was deleted. APPENDIX C EMBED-

DED SOFTWARE