460

CHAPTER 19 SERIAL INTERFACE CHANNEL 2

(3) UART mode cautions

(a) If bit 7 (TXE) of the asynchronous serial interface mode register (ASIM) is cleared to (0) during

transmission and sending operation is halt, be sure to set the transmit shift register (TXS) to FFH, then

set TXE to 1 before executing the next transmission.

(b) If bit 6 (RXE) of ASIM is cleared (0) during reception and receiving operation is halt, the status of the receive

buffer register (RXB) and whether or not a receive completion interrupt (INTSR) is generated differ

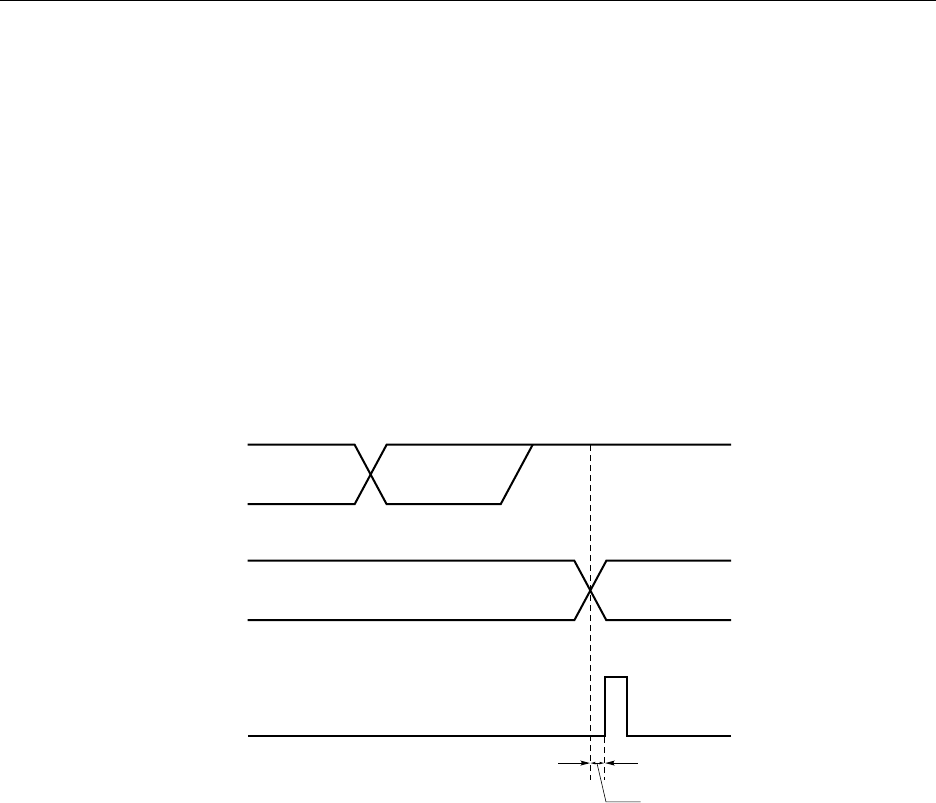

depending on the timing. The timing is shown in Figure 19-11.

Figure 19-11. Receive Buffer Register (RXB) Status and Receive Completion Interrupt

Request (INTSR) Generation When Receiving Is Terminated

ParityRxD Pin

RXB

INTSR

<3><1>

<2>

When RXE is set to 0 at a time indicated by <1>, RXB holds the previous data and does not generate INTSR.

When RXE is set to 0 at a time indicated by <2>, RXB renews the data and does not generate INTSR.

When RXE is set to 0 at a time indicated by <3>, RXB renews the data and generates INTSR.