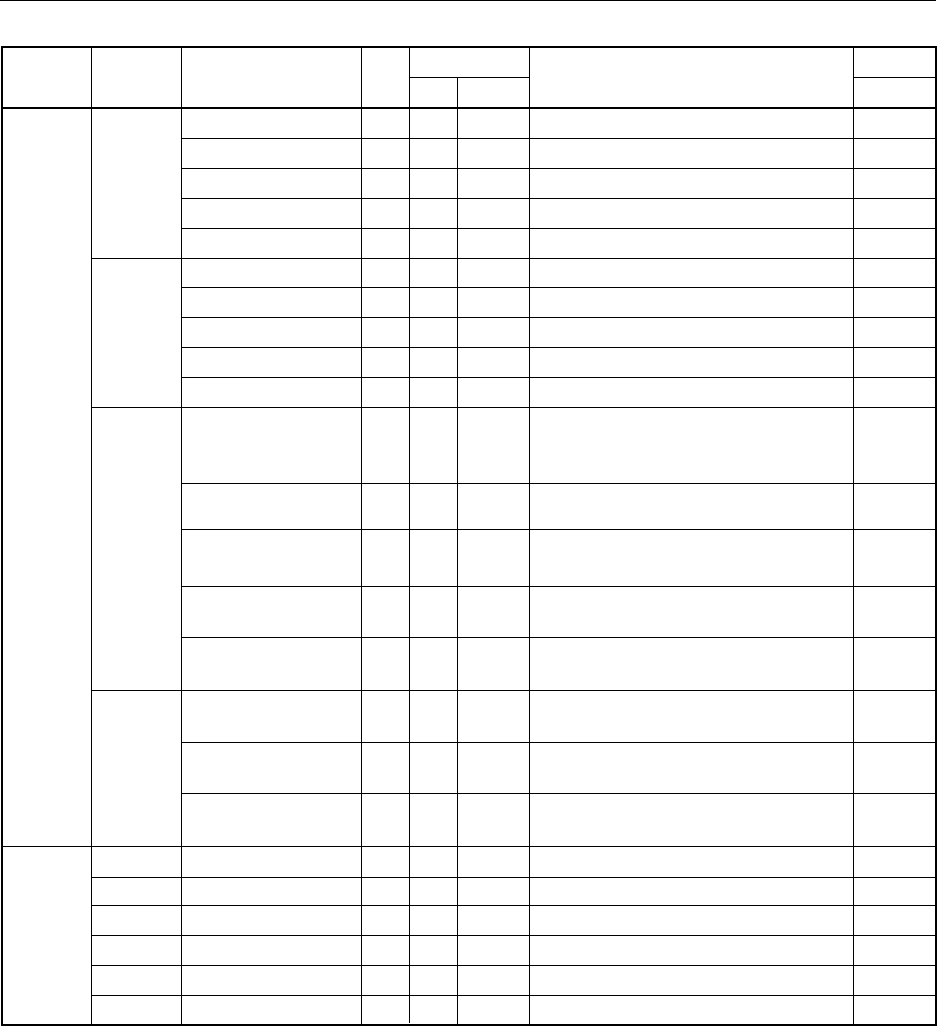

559

CHAPTER 27 INSTRUCTION SET

Clock Flag

Note 1 Note 2

ZACCY

saddr.bit, $addr16 3 8 9 PC ← PC + 3 + jdisp8 if(saddr.bit) = 1

sfr.bit, $addr16 4 – 11 PC ← PC + 4 + jdisp8 if sfr.bit = 1

BT A.bit, $addr16 3 8 – PC ← PC + 3 + jdisp8 if A.bit = 1

PSW.bit, $addr16 3 – 9 PC ← PC + 3 + jdisp8 if PSW.bit = 1

[HL].bit, $addr16 3 10 11 + n PC ← PC + 3 + jdisp8 if (HL).bit = 1

saddr.bit, $addr16 4 10 11 PC ← PC + 4 + jdisp8 if(saddr.bit) = 0

sfr.bit, $addr16 4 – 11 PC ← PC + 4 + jdisp8 if sfr.bit = 0

BF A.bit, $addr16 3 8 – PC ← PC + 3 + jdisp8 if A.bit = 0

PSW.bit, $addr16 4 – 11 PC ← PC + 4 + jdisp8 if PSW. bit = 0

[HL].bit, $addr16 3 10 11 + n PC ← PC + 3 + jdisp8 if (HL).bit = 0

PC ← PC + 4 + jdisp8

saddr.bit, $addr16 4 10 12 if(saddr.bit) = 1

then reset(saddr.bit)

PC ← PC + 4 + jdisp8 if sfr.bit = 1

then reset sfr.bit

BTCLR PC ← PC + 3 + jdisp8 if A.bit = 1

then reset A.bit

PC ← PC + 4 + jdisp8 if PSW.bit = 1

then reset PSW.bit

PC ← PC + 3 + jdisp8 if (HL).bit = 1

then reset (HL).bit

B ← B – 1, then

PC ← PC + 2 + jdisp8 if B ≠ 0

C ← C –1, then

PC ← PC + 2 + jdisp8 if C ≠ 0

(saddr) ← (saddr) – 1, then

PC ← PC + 3 + jdisp8 if(saddr) ≠ 0

SEL RBn 2 4 – RBS1, 0 ← n

NOP 1 2 – No Operation

EI 2 – 6 IE ← 1(Enable Interrupt)

DI 2 – 6 IE ← 0(Disable Interrupt)

HALT 2 6 – Set HALT Mode

STOP 2 6 – Set STOP Mode

Notes 1. When the internal high-speed RAM area is accessed or instruction with no data access

2. When an area except the internal high-speed RAM area is accessed

Remarks 1. One instruction clock is the length of 1 clock cycle of the CPU clock (f

CPU) selected by the processor

clock control register (PCC).

2. This clock cycle applies to internal ROM program.

Mnemonic Operands Byte Operation

Instruction

Group

CPU

control

Condi-

tional

branch

sfr.bit, $addr16 4 – 12

A.bit, $addr16 3 8 –

PSW.bit, $addr16 4 – 12 ×××

[HL].bit, $addr16 3 10

12 + n + m

B, $addr16 2 6 –

DBNZ C, $addr16 2 6 –

saddr. $addr16 3 8 10