47

CHAPTER 2 OUTLINE (

µ

PD78058FY SUBSERIES)

2.1 Features

Compared to the conventional

µ

PD78054Y Subseries, EMI (Electro Magnetic Interference) noise has been

reduced.

On-chip high-capacity ROM and RAM

Notes 1. The capacities of internal PROM and internal high-speed RAM can be changed by means of the

memory size switching register (IMS).

2. The capacity of internal expansion RAM can be changed by means of the internal expansion RAM

size switching register (IXS).

External Memory Expansion Space: 64 Kbytes

Minimum instruction execution time changeable from high speed (0.4

µ

s: In main system clock 5.0 MHz operation)

to ultra-low speed (122

µ

s: In subsystem clock 32.768 kHz operation)

Instruction set suited to system control

• Bit manipulation possible in all address spaces

• Multiply and divide instructions

I/O ports: 69 (N-ch open-drain ports: 4)

8-bit resolution A/D converter: 8 channels

8-bit resolution D/A converter: 2 channels

Serial interface: 3 channels

• 3-wire serial I/O/2-wire serial I/O/I

2

C bus mode: 1 channel

• 3-wire serial I/O mode (Automatic transmit/receive function): 1 channel

• 3-wire serial I/O/UART mode: 1 channel

Timer: 5 channels

• 16-bit timer/event counter : 1 channel

• 8-bit timer/event counter : 2 channels

• Watch timer : 1 channel

• Watchdog timer : 1 channel

22 vectored interrupts

Two test inputs

Two types of on-chip clock oscillators (main system clock and subsystem clock)

Supply voltage: VDD = 2.7 to 6.0 V

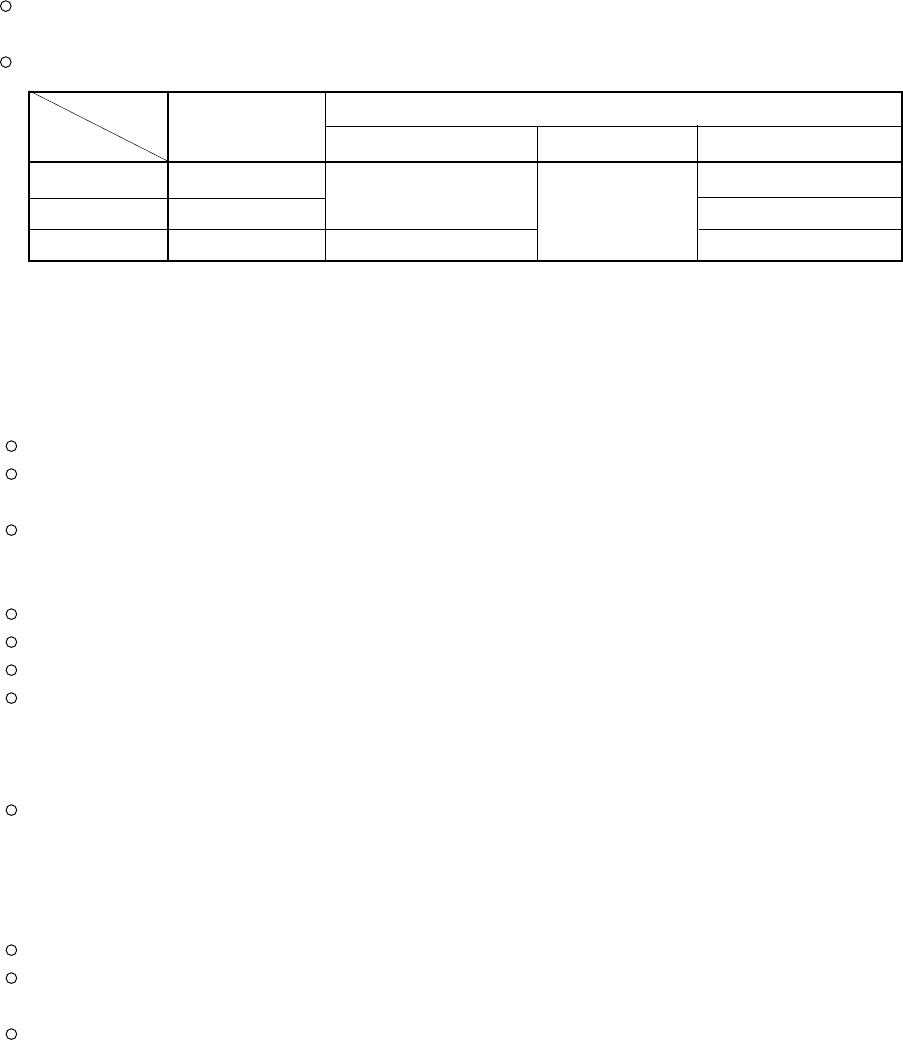

Program Memory

(ROM)

Data Memory

Part Number

Item

µ

PD78056FY

µ

PD78058FY

µ

PD78P058FY

48 Kbytes

60 Kbytes

60 Kbytes

Note 1

1024 bytes 32 bytes None

1024 bytes

1024 bytes

Note 1

1024 byes

Note 2

Internal High-Speed RAM Internal Buffer RAM Internal Expansion RAM