120 AMD Geode™ LX Processors Data Book

CPU Core Register Descriptions

33234H

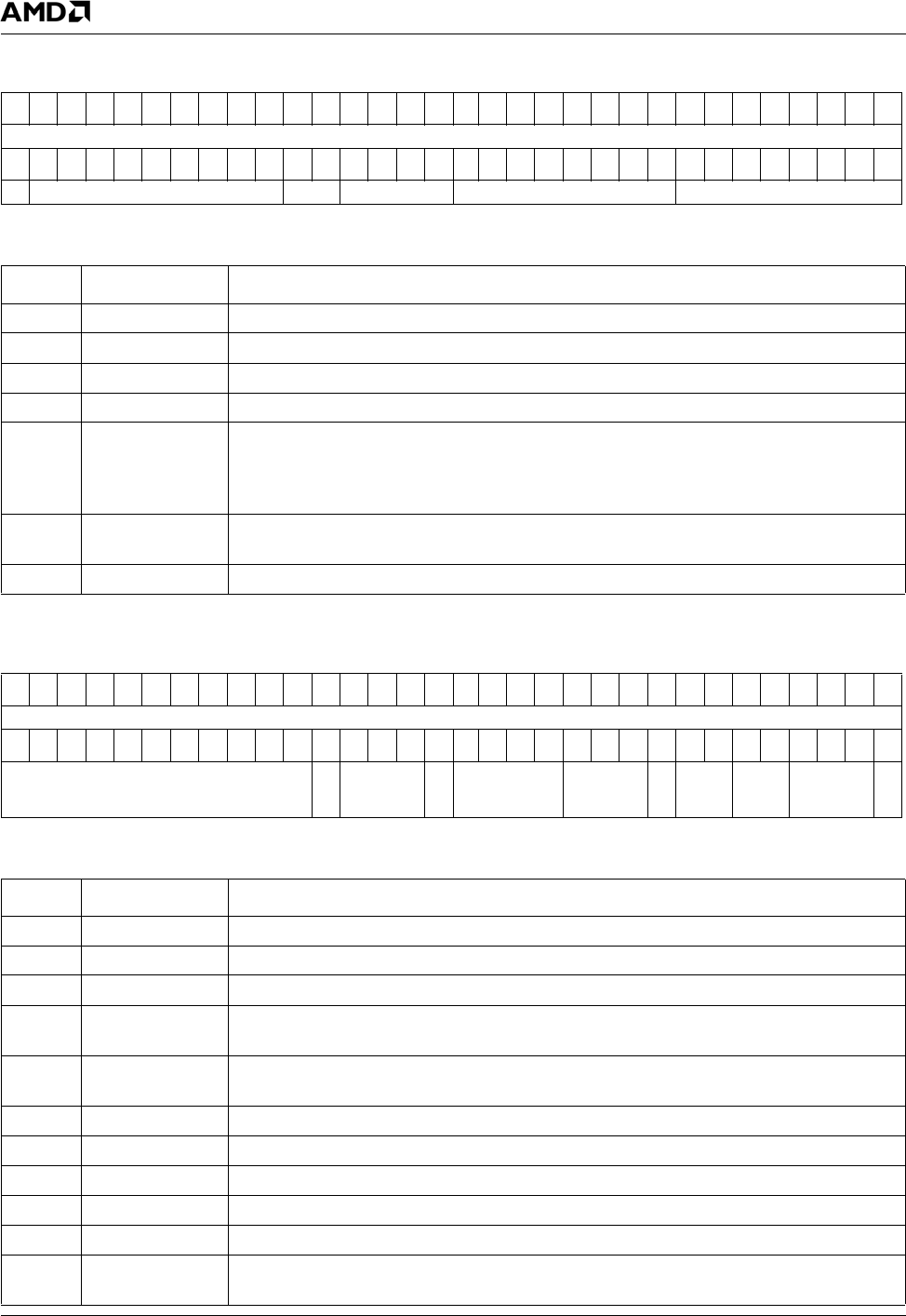

IF_TEST_DATA_MSR Register Map for Tag RAMs

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

V LIP RSVD STRENGTH TYPE END

IF_TEST_DATA_MSR Bit Descriptions for Tag RAMs

Bit Name Description

63:32 RSVD Reserved.

31 V Tag is Valid. (Default = 0)

30:22 LIP Linear Address Bits [19:11].

21:20 RSVD Reserved.

19:16 STRENGTH Prediction Strength. Bit 19 = STRENGTH3, bit 18 = STRENGTH2, bit 17 =

STRENGTH1, and bit 16 = STRENGTH0.

0: Weakly predicted.

1: Strongly predicted.

15:8 TYPE COF Type. Bits [15:14] = TYPE3, bits [13:12] = TYPE2, bits [11:10] = TYPE1, and bits

[9:8] = TYPE0.

7:0 END Predicted Taken COF End Markers.

IF_TEST_DATA_MSR Register Map for Level-0 COF Cache Tag

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

RSVD

PNTKN

RSVD

VLD

LEN RSVD

PTKN

RSVD TYPE RSVD

LRU

IF_TEST_DATA_MSR Bit Descriptions for Level-0 COF Cache Tag

Bit Name Description

63:21 RSVD Reserved.

20 PNTKN Predicted Not Taken. Entry ends with a predicted not-taken change of flow.

19:17 RSVD Reserved.

16 VLD Valid. If an entry is valid, then all the tag information as well as the entry’s address and

target must also be valid. (Default = 0)

15:12 LEN Number of Bytes. Number of bytes from address to either end of QWORD or end of pre-

dicted taken change of flow (0-8).

11:9 RSVD Reserved.

8 PTKEN Predicted Taken. Entry ends with a predicted taken change of flow.

7:6 RSVD Reserved.

5:4 TYPE Change of Flow Type.

3:1 RSVD Reserved.

0LRU Next Entry. Indicates that entry is the next entry to be written. Exactly one of the four

entries should have this bit set.