476 AMD Geode™ LX Processors Data Book

Video Input Port

33234H

6.9.10.1 Video Data Buffers

Video data buffers can be organized in linear or planar for-

mats. Linear buffers pack YUV values contiguous in mem-

ory. Planar buffers have separate subbuffers for each set of

YUV values in a field or frame. The VIP Control 1 register

(VIP Memory Offset 00h[4]) determines if the video storage

format is linear or planar.

In linear format, the first video line is stored beginning at

the vid_base address, the second line is stored beginning

at vid_base + pitch, the third line at task_base + (2 x pitch)

and so on until the end of the field/frame. See Figure 6-51

on page 477 for an example of a 4:2:2 SAV/EAV packets

stored in system memory in a linear format.

In planar format, the Y buffer begins at the task_base

address, the U buffer begins at the (vid_base +

U_buffer_offset), and the V values start at the (vid_base +

V_buffer_offset). The pitch value for Y is vid_pitch. The

pitch value for V and U is task_A_UV_pitch (for Task A UV

data) or task_b_pitch/2 (Task b UV data). In 4:2:2 or 4:2:0

video, there are twice as many Y data values per line as

there are U or V values. Additional odd/even offsets and

pitch registers are provided for Task A data. Input U/V val-

ues can be decimated (even lines or even fields). This fur-

ther reduces the U and V data to 1/4 of the Y data.

See Figure 6-51 on page 477 and Figure 6-52 on page 478

for examples of SAV/EAV packets stored in linear buffer

and planar buffer format.

6.9.10.2 VBI Data Buffers

The VBI data packets are stored in linear format. VBI data

is essentially a line of video that occurs during vertical

blanking. The first VBI line is stored beginning at vbi_base,

the second line is stored beginning at vbi_base + vid_pitch,

the third line at vbi_base + (2 x vid_pitch) and on until the

end of the vertical blanking period.

6.9.10.3 Ancillary Data Buffers

Ancillary data packets are stored starting at the buffer

address defined by anc_msg_1. Packet storage continues

to address anc_msg_1 + anc_msg_size at which point the

address is wrapped back around to anc_msg_1. When a

new packet is received, the packet count is incremented.

When software reads a packet from the buffer, it decre-

ments the count by writing a 1 to the Decrement Ancillary

Packet Count bit in the VIP Status register (VIP Memory

Offset 08h[18]).

Ancillary data packets include a checksum. After packet

reception, the internally generated checksum is compared

to the checksum sent with the ancillary packet. If these val-

ues do not compare, the packet is marked bad by writing a

F0 in fill byte immediately following the checksum byte (8/

16 ancillary data) or a 1111 in bits [15:12] of the checksum

DWORD for 10-bit ancillary data. Parity checking is also

performed on the DID, SDID, NN, and checksum WORDs.

Packets with parity errors set the same error bits as when a

checksum error occurs. Parity and checksum errors are

reported in the VIP Status register (VIP Memory Offset

08h). They share a status bit. Parity checking can be dis-

abled via the ANCPEN bit in Control Register 2 (VIP Mem-

ory Offset 04h[26]).

Figure 6-53 on page 479 shows an example of ancillary

packets stored in system memory.

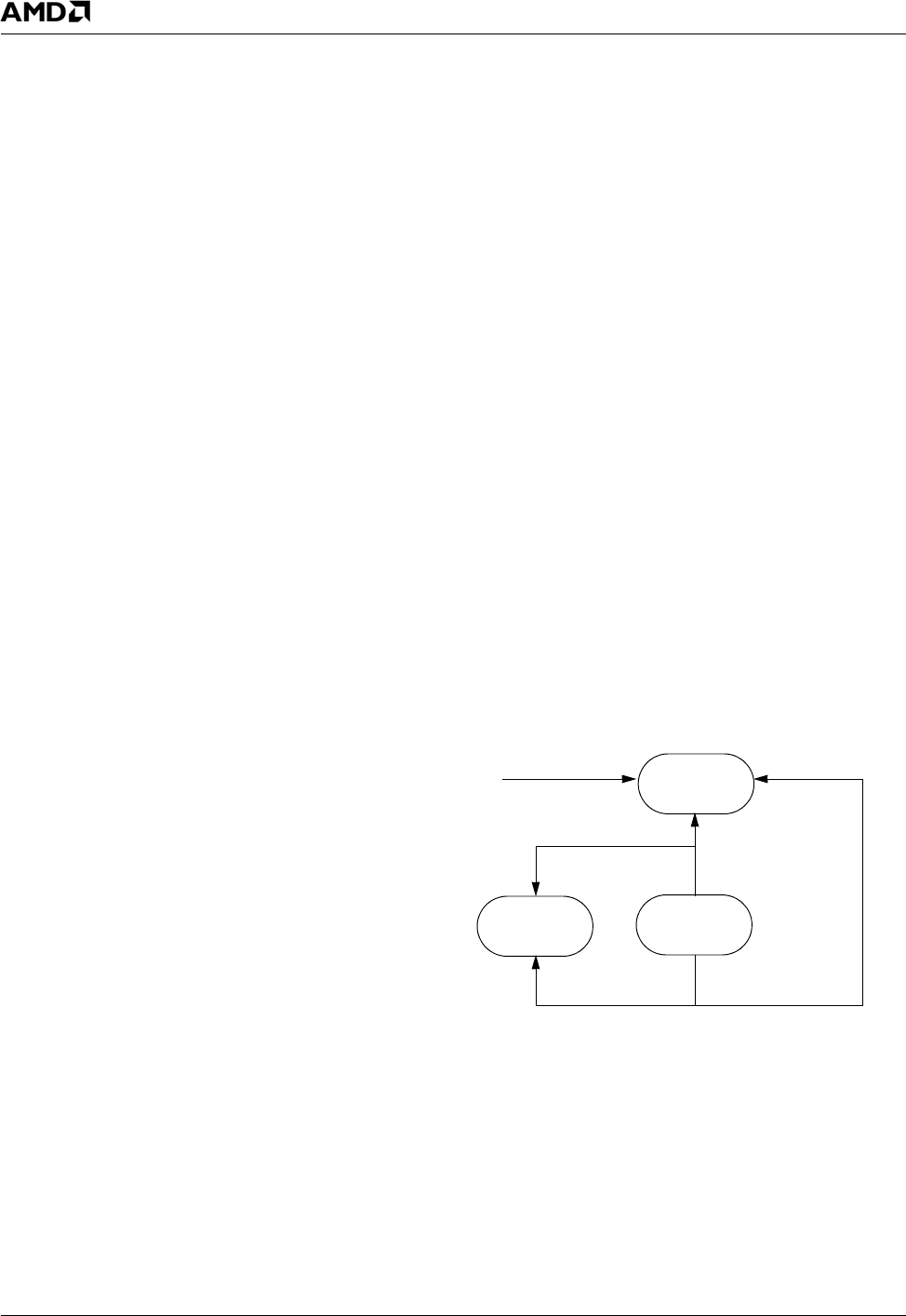

6.9.10.4 Message Passing/Data Streaming Modes

The MSG and STRM modes provide a mechanism for the

AMD Geode CS5536 companion device to send raw data

to the AMD Geode LX processor system memory. MSG

and STRM modes have identical software models. Two

buffers are used (see Figure 6-50). The

VIP_ANC_MSG_1_BASE and VIP_ANC_MSG_2_BASE

registers (VIP Memory Offset 58h and 5Ch) define the two

buffer locations. The VIP_ANC_MSG_SIZE register (VIP

Memory Offset 60h) defines the maximum size of each

buffer. The first packet (data associated with a Start/End

indication) is saved starting at msg_1_base address. The

MB bit in Control Register 1 (VIP Memory Offset 00h[18])

determines when buffer swapping occurs. When MB = 0,

buffers are swapped each packet. When MB = 1, buffers

are only swapped when full. This mode might be used if a

continuous data stream is being delivered. A Message

Buffer Full interrupt occurs when a buffer swap occurs.

Software can read the VIP Status register to determine

which buffer or buffers are full. Software must reset the bit

in order for the buffer to become available. The MSG Buffer

Error status bit (bit 14) is set when a buffer swap occurs

from buffer 1 to buffer 2 with buffer 2 being unavailable or if

a buffer swap occurs from buffer 2 to buffer 1 with buffer 1

being unavailable.

Figure 6-50. Dual Buffer for Message Passing

and Data Streaming Modes

Buffer 1

in use

Buffer 2

in use

buffer1_full/

buffer2_full

Buffer

overrun

buffer2_full

buffer1_full

buffer2_full#

buffer1_full#

mode_2 or mode_3

new PKT

or new PKT