416 AMD Geode™ LX Processors Data Book

Video Processor Register Descriptions

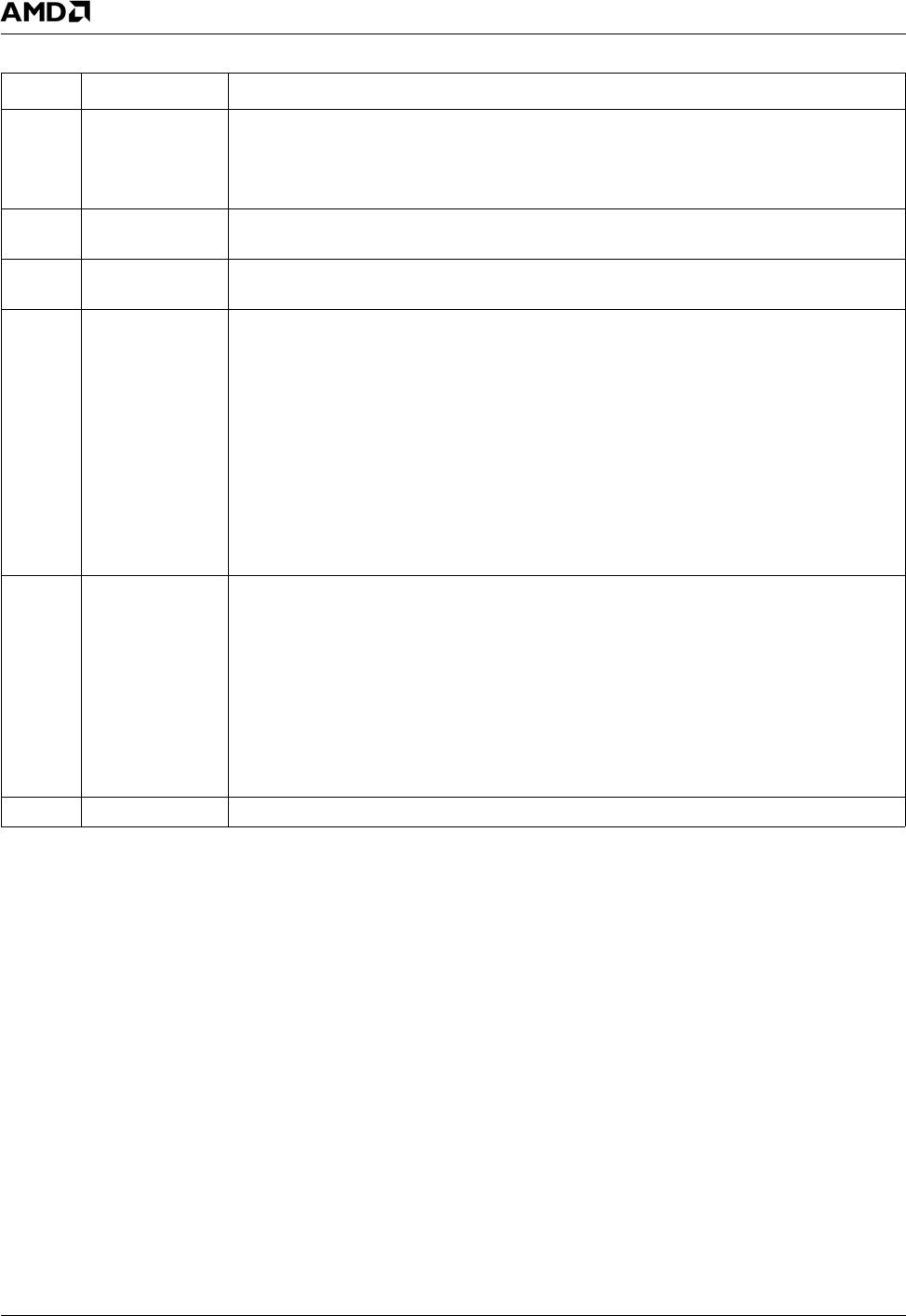

33234H

15 FPC Simultaneous Flat Panel (or VOP) and CRT. Primary display is flat panel. Setting this

bit activates the CRT DAC interface to allow simultaneous display of both panel and

CRT. Leaving this bit reset forces the CRT DAC signals to zero.

This bit is ignored if bits [5:3] of this register are set to 0 or 4.

14 IUV Interchange UV. Interchange byte order of the U and V bytes (see bits [7:6]). This

applies only to DRGB mode (see bits [5:3]).

13:8 DIV Clock Divider. GLIU clock divider to produce 14.3 MHz reference clock. Result must be

equal to or less than 14.3 MHz. GLIU clock speed/DIV = reference clock.

7:6 FMTBO Format Byte Order. The lower 24 bits of the DRGB output bus byte order can be modi-

fied for any required interface. These bits, along with bit 14, are used to output the follow-

ing combinations of byte order. This applies only to DRGB mode.

000 = RGB / YUV (YC

b

C

r

)

001 = BGR / VUY (C

r

C

b

Y)

010 = BGR / VYU (C

r

YC

b

)

011 = BRG / VUY (C

r

C

b

Y)

100 = RGB / YVU (YC

r

C

b

)

101 = BGR / VYU (C

r

YC

b

)

110 = BGR / VUY (C

r

C

b

Y)

111 = BRG / VYU (C

r

YC

b

)

5:3 FMT VP Output Format Select. Video Processor module display outputs formatted for CRT

or flat panel. Resets to CRT; software must change if a different mode is required.

000: CRT.

001: Flat Panel.

010: Reserved.

011: Reserved.

100: CRT Debug mode.

101: Reserved.

110: VOP.

111: DRGB.

2:0 PID VP Priority Domain. Video Processor module assigned priority domain identifier.

GLD_MSR_CONFIG Bit Descriptions (Continued)

Bit Name Description