202 AMD Geode™ LX Processors Data Book

CPU Core Register Descriptions

33234H

5.5.2.114 FPU Modes MSR (FP_MODE_MSR)

5.5.2.115 FPU Reserved MSR (FPU_RSVD_MSR)

This register is reserved for internal testing; do not write.

5.5.2.116 FPU Reserved MSR (FPU_RSVD_MSR)

This register is reserved for internal testing; do not write.

MSR Address 00001A00h

Typ e R /W

Reset Value 00000000_00000000h

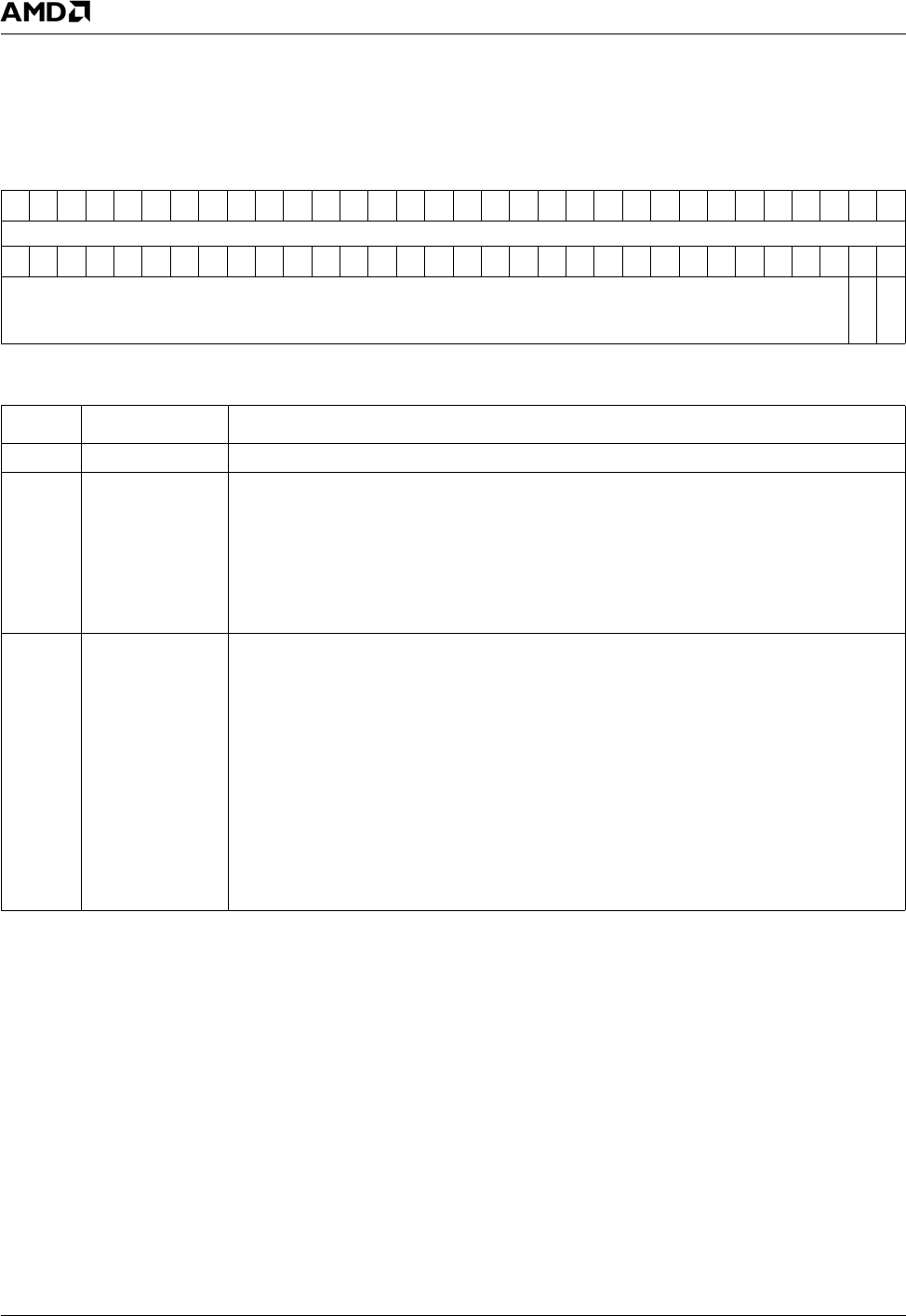

FP_MODE_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

RSVD

FPU_SP

FPU_IPE

FP_MODE_MSR Bit Descriptions

Bit Name Description

63:2 RSVD Reserved. Write as read.

1FPU_SP Limit Results to Single Precision. The FPU datapath width is single-precision. Opera-

tions on single precision numbers can generally be completed in one cycle, but double or

extended precision numbers takes many cycles. This bit overrides the precision control

bits in the x87 Mode Control register (of the FPU Instruction Set), and causes the FPU to

operate as if the precision control is set to single precision (00).

0: Disable.

1: Enable limit to single precision.

0 FPU_IPE Enable Force of Imprecise Exceptions. For precise exceptions, the FPU allows only

one instruction to be in the pipeline at a time when any FPU exceptions are unmasked.

This results in a huge performance penalty. To run the FPU at full speed, it is necessary

to mask all exceptions in the FPU_CW_MSR (MSR 00001A10h[11:0]).

When this bit is set, the FPU is allowed to run at full speed even if there are unmasked

exceptions in the FPU_CW. With this bit set, exceptions will be generated, however,

there is no guarantee that the exception will occur on any particular instruction boundary.

It is known that setting this bit will cause some diagnostic software to fail. It is recom-

mended to be set only when the FPU exception handler does not need to handle excep-

tions on the specific instruction boundary.

0: Disable.

1: Enable.

MSR Address 00001A01h

Typ e R /W

Reset Value 00000000_00000000h

MSR Address 00001A03h

Typ e R /W

Reset Value 00000000_00000000h