AMD Geode™ LX Processors Data Book 161

CPU Core Register Descriptions

33234H

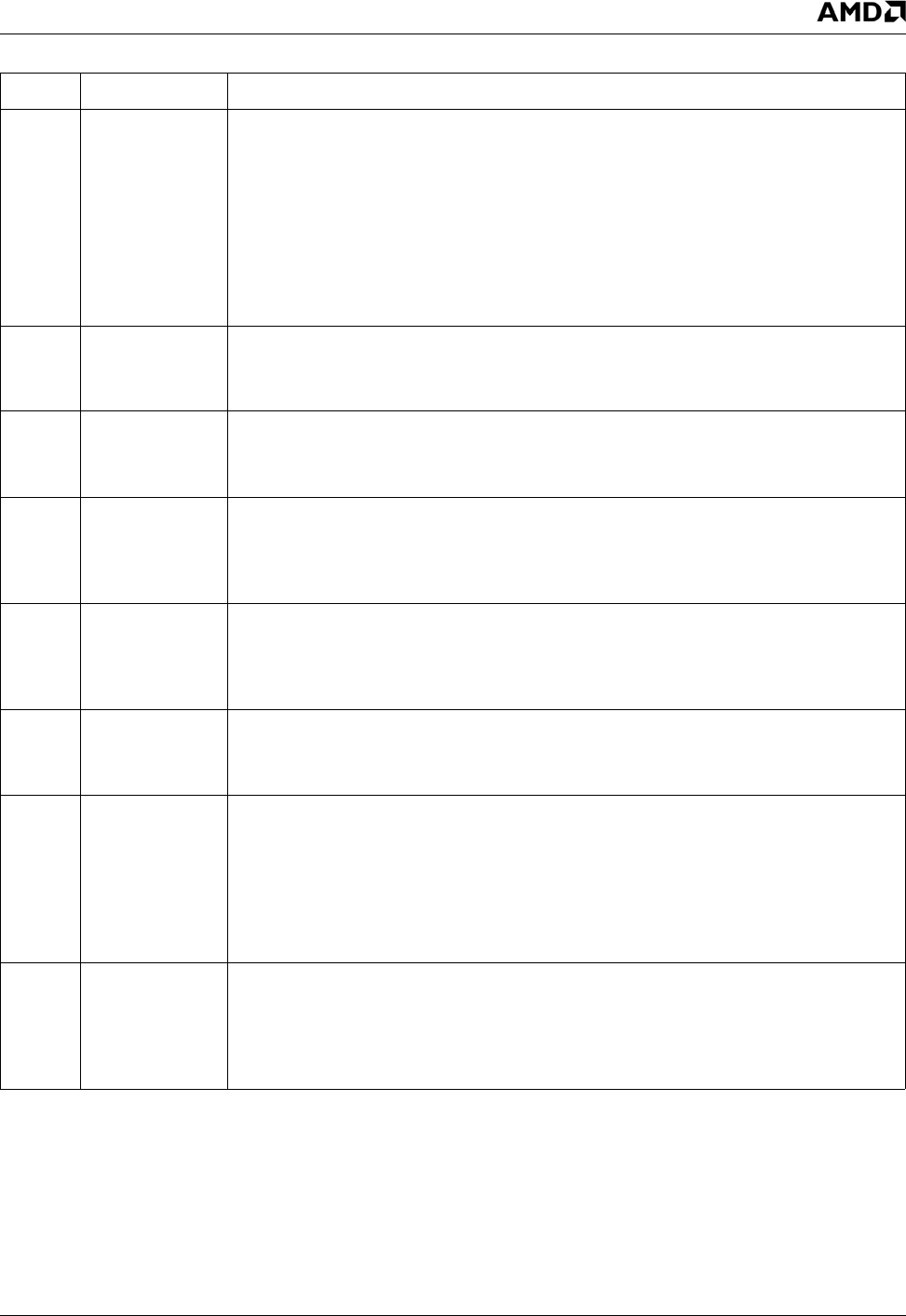

7 SPCDEC Decrease Number of Speculative Reads of Data Cache.

0: Actively resync cache tag and data arrays so that loads can be speculatively handled

in one clock if the MRU way is hit. (Default)

1: Do not attempt to resync cache tag and data arrays.

This is a performance optimization bit and the preferred value may have to be empirically

determined. The cache tag and data arrays get “out of sync” when there is a miss to the

MRU way or if the data array is busy with a store, linefill, or eviction. While the arrays are

out of sync, all hits take 2 clocks. When they are in sync, hits to the MRU way take 1

clock while hits to other ways take 3.

6WTBRST Write-Through Bursting.

0: Writes are sent unmodified to the bus on write-through operations. (Default)

1: Writes may be combined using write-burstable semantics on write-through operations.

5WBINVD Convert INVD to WBINVD Instruction.

0: INVD instruction invalidates cache without writeback. (Default)

1: INVD instruction writes back any dirty cache lines

4NOSMC Snoop Detecting on Self-Modified Code. Generates snoops on stores for detecting

self-modified code.

0: Generate snoops. (Default)

1: Disable snoops.

3NOFWD Forward Data from Bus Controller. Enable forwarding of data directly from bus control-

ler if a new request hits a line fill in progress.

0: Forward data from bus controller if possible. (Default)

1: Wait for valid data in cache, then read cache array.

2BLOCKC Blocking Cache.

0: New request overlapped with linefill. (Default)

1: Linefill must complete before starting new request.

1 MISSER Serialize Load Misses. Stall everything but snoops on a load miss. Set this bit if part of

PCI space is marked as cacheable (e.g., for a ROM), data accesses will be made from

that cacheable space, and there is a PCI master device which must complete a master

request before it will complete a slave read.

0: Load misses are treated the same as load hits. (Default)

1: Load misses prevent non-snoop requests from being handled until the miss data is

returned by the bus controller.

0 LDSER Serialize Loads vs Stores. All loads are serialized versus stores in the store queue, but

a load that hits the cache completes without affecting any pending stores in the write

buffers.

0: Loads bypass stores based on region properties. (Default)

1: All loads and stores are executed in program order.

DM_CONFIG0_MSR Bit Descriptions (Continued)

Bits Name Description