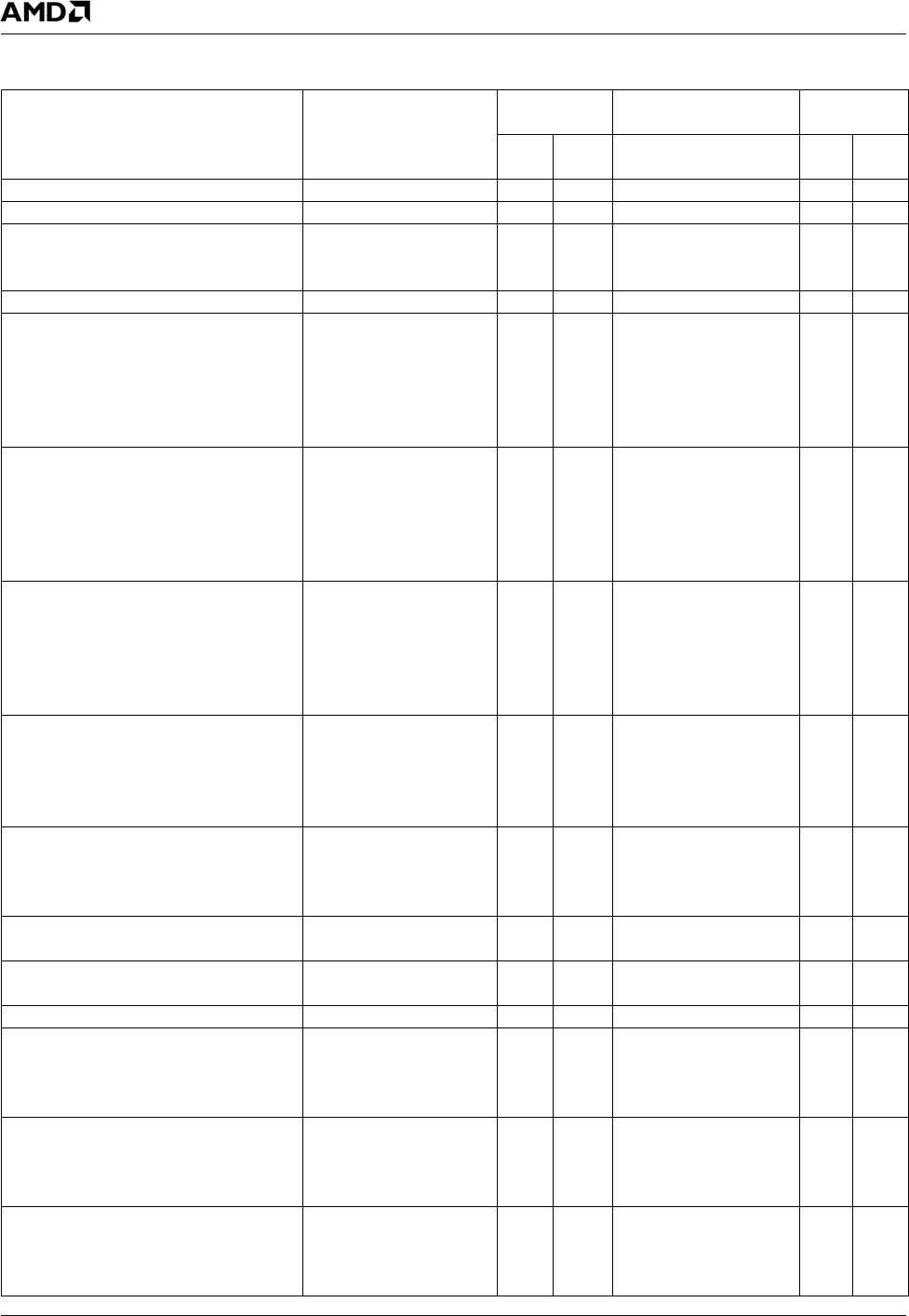

634 AMD Geode™ LX Processors Data Book

Instruction Set

33234H

Table 8-26. Processor Core Instruction Set

Instruction Opcode

Clock Count

(Reg/Cache Hit) Flags

Notes

Real

Mode

Prot’d

Mode

ODI TSZ APC

FFFFFFFFF

Real

Mode

Prot’d

Mode

AAA ASCII Adjust AL after Addition 37 3 3 u -- -uuxux

AAD ASCII Adjust AX before Divide D5 0A 4 4 u---xxuxu

AAM ASCII Adjust AX after Multiply D4 0A u---xxuxu

Divide by non-zero 15 15

Divide by zero 18 18

AAS ASCII Adjust AL after Subtract 3F 3 3 u- - - uuxux

ADC Add with Carry x---xxxxx b h

Register to Register 1 [00dw] [11 reg r/m] 1 1

Register to Memory 1 [000w] [mod reg r/m] 1 1

Memory to Register 1 [001w] [mod reg r/m] 1 1

Immediate to Register/Memory 8 [00sw] [mod 010 r/m]### 1 1

Immediate to Accumulator 1 [010w] ### 1 1

ADD Integer Add x---xxxxx b h

Register to Register 0 [00dw] [11 reg r/m] 1 1

Register to Memory 0 [000w] [mod reg r/m] 1 1

Memory to Register 0 [001w] [mod reg r/m] 1 1

Immediate to Register/Memory 8 [00sw] [mod 000 r/m]### 1 1

Immediate to Accumulator 0 [010w] ### 1 1

AND Boolean AND 0---xxux0 b h

Register to Register 2 [00dw] [11 reg r/m] 1 1

Register to Memory 2 [000w] [mod reg r/m] 1 1

Memory to Register 2 [001w] [mod reg r/m] 1 1

Immediate to Register/Memory 8 [00sw] [mod 100 r/m]### 1 1

Immediate to Accumulator 2 [010w] ### 1 1

ARPL Adjust Requested Privilege Level 63 [mod reg r/m] -----x--- ah

To Memory DST[1:0] < SRC[1:0] 6

To Memory DST[1:0] >= SRC[1:0] 4

To Register DST[1:0] < SRC[1:0] 4

To Register DST[1:0] >= SRC[1:0] 4

BOUND Check Array Boundaries 62 [mod reg r/m] --------- b, e g,h,j,k,

r

If Below Range (Interrupt #5) 8+INT 8+INT

If Above Range (Interrupt #5) 8+INT 8+INT

If In Range 66

BSF Scan Bit Forward 0F BC [mod reg r/m] 2 2 -----x--- b h

Register, Register/Memory

BSR Scan Bit Reverse 0F BD [mod reg r/m] 2 2 -----x--- b h

Register, Register/Memory

BSWAP Byte Swap 0F C[1 reg] 1 1 ---------

BT Test Bit --------x b h

Register/Memory, Immediate 0F BA [mod 100 r/m]# 1 1

Register, Register 0F A3 [mod reg r/m] 1 1

Memory, Register 0F A3 [mod reg r/m] 7 7

BTC Test Bit and Complement --------x b h

Register/Memory, Immediate 0F BA [mod 111 r/m]# 2 2

Register, Register 0F BB [mod reg r/m] 2 2

Memory, Register 0F BB [mod reg r/m] 8 8

BTR Test Bit and Reset --------x b h

Register/Memory, Immediate 0F BA [mod 110 r/m]# 2 2

Register, register 0F B3 [mod reg r/m] 2 2

Memory, Register 0F B3 [mod reg r/m 8 8