AMD Geode™ LX Processors Data Book 451

Video Processor Register Descriptions

33234H

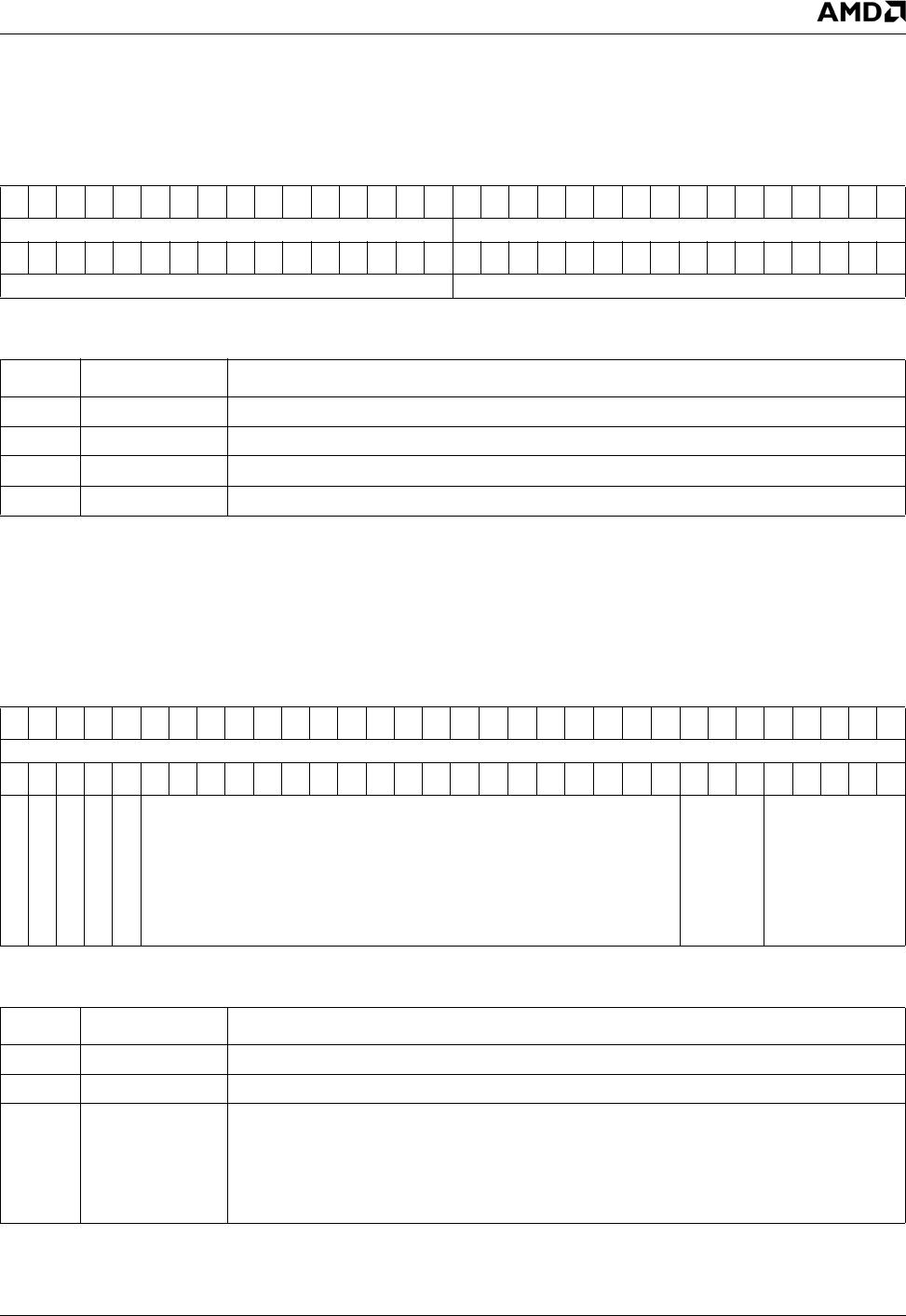

6.8.3.42 Video Coefficient RAM (VCR)

6.8.3.43 Panel Timing Register 1 (PT1)

VP Memory Offset 1000h-1FFFh

Typ e R /W

Reset Value xxxxxxxx_xxxxxxxxh

VCR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

VC3 VC2

313029282726252423222120191817161514131211109876543210

VC1 VC0

VCR Bit Descriptions

Bit Name Description

63:48 VC3 Coefficient 3. Coefficient for tap 3 of filter.

47:32 VC2 Coefficient 2. Coefficient for tap 2 of filter.

31:16 VC1 Coefficient 1. Coefficient for tap 1 of filter.

15:0 VC0 Coefficient 0. Coefficient for tap 0 of filter.

VP Memory Offset 400h

Typ e R /W

Reset Value 00000000_00000000h

PT1 Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

RSVD

FP_VSYNC_POL

FP_HSYNC_POL

RSVD

HSYNC_SRC

RSVD

HSYNC_DELAY

HSYNC_PLS_WIDTH

PT1 Bit Descriptions

Bit Name Description

63:32 RSVD (RO) Reserved (Read Only). Reads back as 0.

31 RSVD Reserved. This bit is not defined.

30 FP_VSYNC_

POL

FP_VSYNC Input Polarity. Selects positive or negative polarity of the FP_VSYNC input.

Program this bit to match the polarity of the incoming FP_VSYNC signal. Note that FP

Memory Offset 408h[23] controls the polarity of the output VSYNC.

0: FP_VSYNC is normally low, transitioning high during sync interval. (Default)

1: FP_VSYNC is normally high, transitioning low during sync interval