662 AMD Geode™ LX Processors Data Book

Instruction Set

33234H

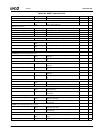

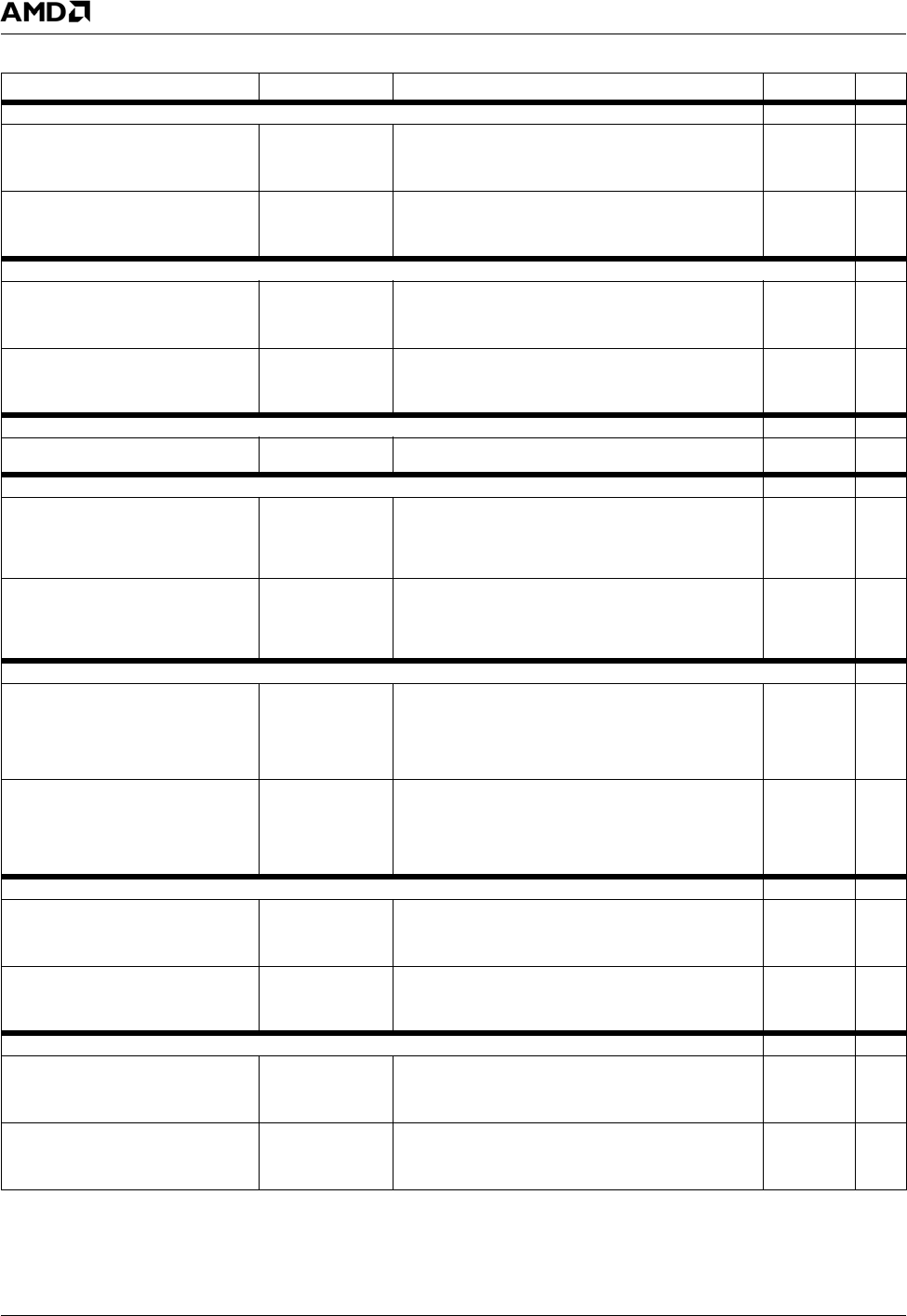

PCMPGTD Pack Compare Greater Than Dword

MMX Register 2 to MMX Register 1 0F66 [11 mm1 mm2] MMX reg 1 [dword] <--- FFFF FFFFh --- if MMX reg 1 [dword]

> MMX reg 2 [dword]

MMX reg 1 [dword]<--- 0000 0000h ---if MMX reg 1

[dword]NOT > MMX reg 2 [dword]

2

Memory with MMX Register 0F66 [mod mm r/m] MMX reg [dword] <--- FFFF FFFFh --- if memory[dword] >

MMX reg [dword]

MMX reg [dword] <--- 0000 0000h --- if memory[dword] NOT

> MMX reg [dword]

2

PCMPGTW Pack Compare Greater Than Word

MMX Register 2 to MMX Register 1 0F65 [11 mm1 mm2] MMX reg 1 [word] <--- FFFFh --- if MMX reg 1 [word] > MMX

reg 2 [word]

MMX reg 1 [word]<--- 0000h --- if MMX reg 1 [word] NOT >

MMX reg 2 [word]

2

Memory with MMX Register 0F65 [mod mm r/m] MMX reg [word] <--- FFFFh --- if memory[word] > MMX reg

[word]

MMX reg [word] <--- 0000h --- if memory[word] NOT > MMX

reg [word]

2

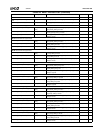

PEXTRW Extract Word into Integer Register 1

Register 32, MMX Register 2 imm8 0FC5 [11 reg mm] # Reg 32 [high word] <--- 0000

reg32 [low word] <--- MMX reg [windex0 (imm8)]

PINSRW Insert Word from Integer Register

MMX Register, Register 32 imm8 0FC4 [11 mm1 reg]

#

tmp1 <--- 0

tmp1 [windex0 (imm8)] <--- reg 32 [low word]

tmp2 <--- MMX reg

tmp2 [windex0 (imm8)] <--- 0

MMX reg <--- tmp 1 Logic OR tmp2

2

MMX Register, Memory 16, imm8 0FC4 [mod mm r/m]

#

temp1 <--- 0

tmp1 [windex0 (imm8)] <--- Memory 16

tmp2 <--- MMX reg

tmp2 [windex0 (imm8)] <--- 0

MMX reg <--- tmp1 Logic OR tmp2 [windex 0 (imm8)]

2

PMADDWD Packed Multiply and Add

MMX Register 2 to MMX Register 1 0FF5 [11 mm1

mm2]

MMX reg 1 [low dword] <--- (MMX reg 1 [low dword] * MMX

reg 2 [low sign word] + (MMX reg 1 [low dword] * MMX reg2

[high sign word]

MMX reg 1 [high dword] <--- (MMX reg 1 [high dword] * MMX

reg 2 [low sign word] + (MMX reg 1 [high dword] * MMX reg2

[high sign word]

2

Memory to MMX Register 0FF5 [mod mm r/m] MMX reg 1 [low dword] <--- (memory [low dword] * MMX reg

[low sign word] + (memory1 [low dword] * MMX reg [high sign

word])

MMX reg 1 [high dword] <--- (memory [higi dword] * MMX reg

[low sign word] + (memory1 [high dword] * MMX reg [high sign

word])

2

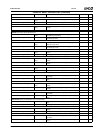

PMAXSW Packed Maximum Signed Word

MMX Register 1 with MMX Register 2 0FEE [11 mm1

mm2]

MMX reg 1 [word] <--- MMX reg 1 [word] --- if (MMX reg 1

[sign word]

> MMX reg 2 [sign word])

MMX reg 1 [word] <--- MMX reg 2 [word] --- if (MMX reg 1

[sign word] NOT

> MMX reg 2 [sign word]

2

MMX Register with Memory64 0FEE [mod mm r/m] MMX reg [word] <--- MMX reg [word] --- if (MMX reg [sign

word]

> Memory64 [word]) MMX reg [word] <--- Memory64

[word] --- if (MMX reg [sign word] NOT

> Memory64 [sign

word]

2

PMAXUB Packed Maximum Unsigned Byte

MMX Register 1 with MMX Register 2 0FDE [11 mm1

mm2]

MMX reg 1 [byte] <--- MMX reg 1 [byte] --- if (MMX reg 1 [byte]

> MMX reg 2 [byte]0

MMX reg 1 [byte] <--- MMX reg 2 [byte] --- if (MMX reg 1 [byte]

NOT

> MMX reg 2 [byte])

2

MMX Register with Memory64 0FDE [mod mm r/m] MMX reg [byte] <--- MMX reg [byte] --- if (MMX reg [byte]

>

Memory64 [byte])

MMX reg [byte] <--- Memory64 [byte] --- if (MMX reg [byte]

NOT

> Memory64 [byte])

2

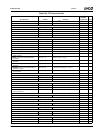

Table 8-28. MMX™ Instruction Set (Continued)

MMX™ Instructions Opcode Operation Clock Ct Notes