164 AMD Geode™ LX Processors Data Book

CPU Core Register Descriptions

33234H

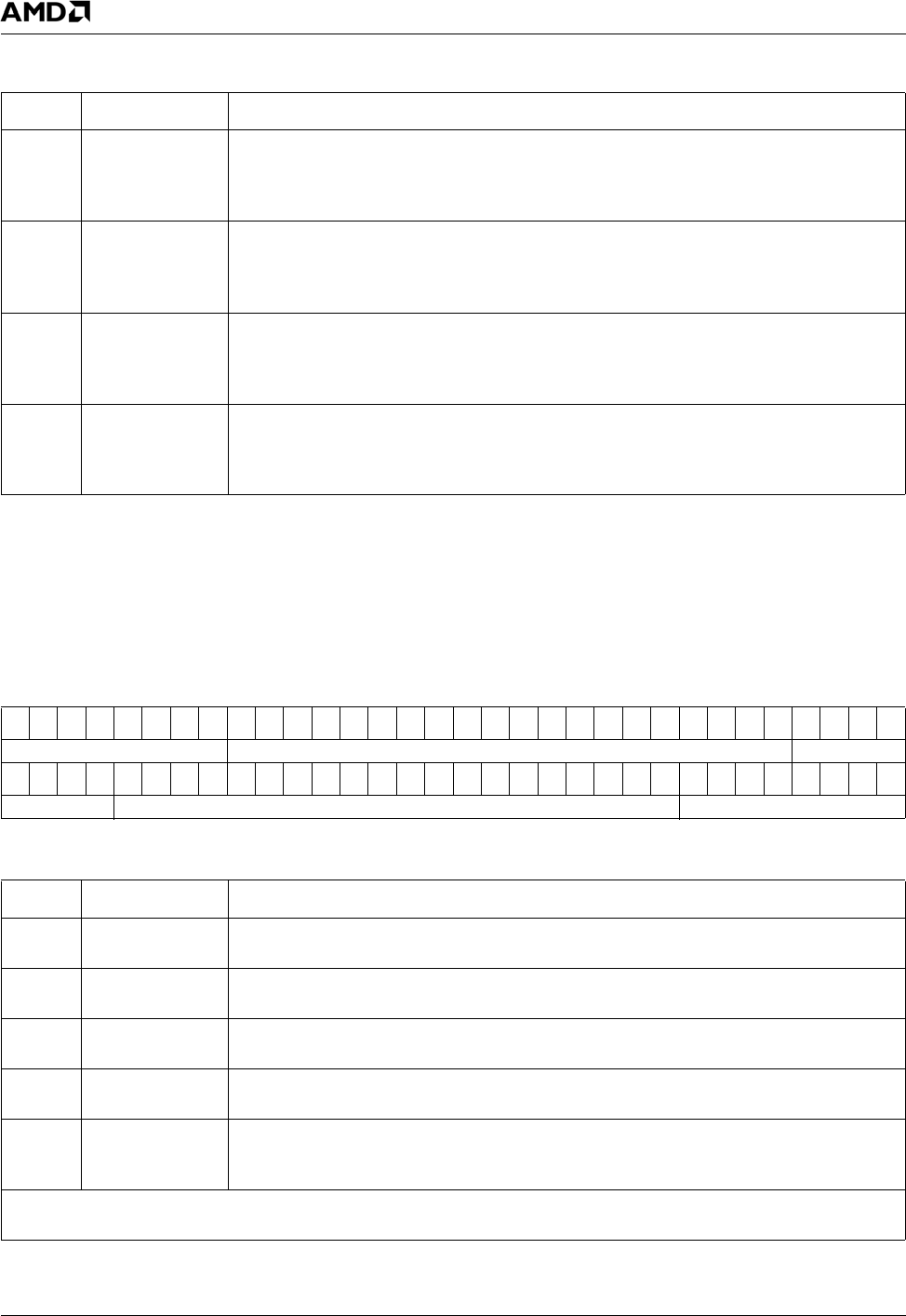

5.5.2.66 Default Region Configuration Properties MSR (RCONF_DEFAULT_MSR)

DM_PFLOCK_MSR Bit Descriptions

Bits Name Description

63:48 PFLOCKT2 Prefetch Lockout of PREFETCHT2. Bit mask of ways that cannot be allocated or

replaced on a data prefetch miss on a PREFECTHT2 instruction. If all ways are locked,

PREFETCHT2 is effectively disabled. Use this field to prevent data prefetch operations

from polluting too much of the cache. (Default = 0)

47:32 PFLOCKT1 Prefetch Lockout of PREFETCHT1. Bit mask of ways that cannot be allocated or

replaced on a data prefetch miss on a PREFECTHT1 instruction. If all ways are locked,

PREFETCHT1 is effectively disabled. Use this field to prevent data prefetch operations

from polluting too much of the cache. (Default = 0)

31:16 PFLOCKT0 Prefetch Lockout of PREFETCHT0. Bit mask of ways that cannot be allocated or

replaced on a data prefetch miss on a PREFECTHT0 instruction. If all ways are locked,

PREFETCHT0 is effectively disabled. Use this field to prevent data prefetch operations

from polluting too much of the cache. (Default = 0)

15:0 PFLOCKNTA Prefetch Lockout of PREFETCHNTA. Bit mask of ways that cannot be allocated or

replaced on a data prefetch miss on a PREFECTHNTA instruction. If all ways are locked,

PREFETCHNTA is effectively disabled. Use this field to prevent data prefetch operations

from polluting too much of the cache. (Default = 0)

MSR Address 00001808h

Typ e R /W

Reset Value 01FFFFF0_10000001h

Warm Start Value 04xxxxx0_1xxxxx01h

RCONF_DEFAULT_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

ROMRP ROMBASE DEVRP

313029282726252423222120191817161514131211109876543210

DEVRP SYSTOP SYSRP

RCONF_DEFAULT_MSR Bit Descriptions

Bit Name Description

63:56 ROMRP ROM Region Properties. Region properties for addresses greater than ROMBASE (bits

55:36]).

55:36 ROMBASE ROM Base Address. Base address for boot ROM. This field represents A[32:12] of the

memory address space, 4 KB granularity.

35:28 DEVRP SYSTOP to ROMBASE Region Properties. Region properties for addresses less than

ROMBASE (bits 55:36]) and addresses greater than or equal to SYSTOP (bits [27:8]).

27:8 SYSTOP Top of System Memory. Top of system memory that is available for general processor

use. The frame buffer and other private memory areas are located above SYSTOP.

7:0 SYSRP System Memory Region Properties. Region properties for addresses less than SYS-

TOP (bits [27:8]). Note that Region Configuration 000A0000h-000FFFFFh takes prece-

dence over SYSRP.

Note: Region Properties: Bits [7:6] = RSVD; Bit 5 = WS; Bit 4 = WC; Bit 3 = WT; Bit 2 = WP; Bit 1 = WA; Bit 0 = CD.

See "Region Properties" on page 170 for further details.