AMD Geode™ LX Processors Data Book 553

GeodeLink™ Control Processor Register Descriptions

33234H

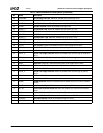

6.14.2.11 GLCP Clock Mask for Debug Clock Stop Action (GLCP_CLKDISABLE)

See "GLCP_CLKOFF Bit Descriptions" on page 551 for bit descriptions.

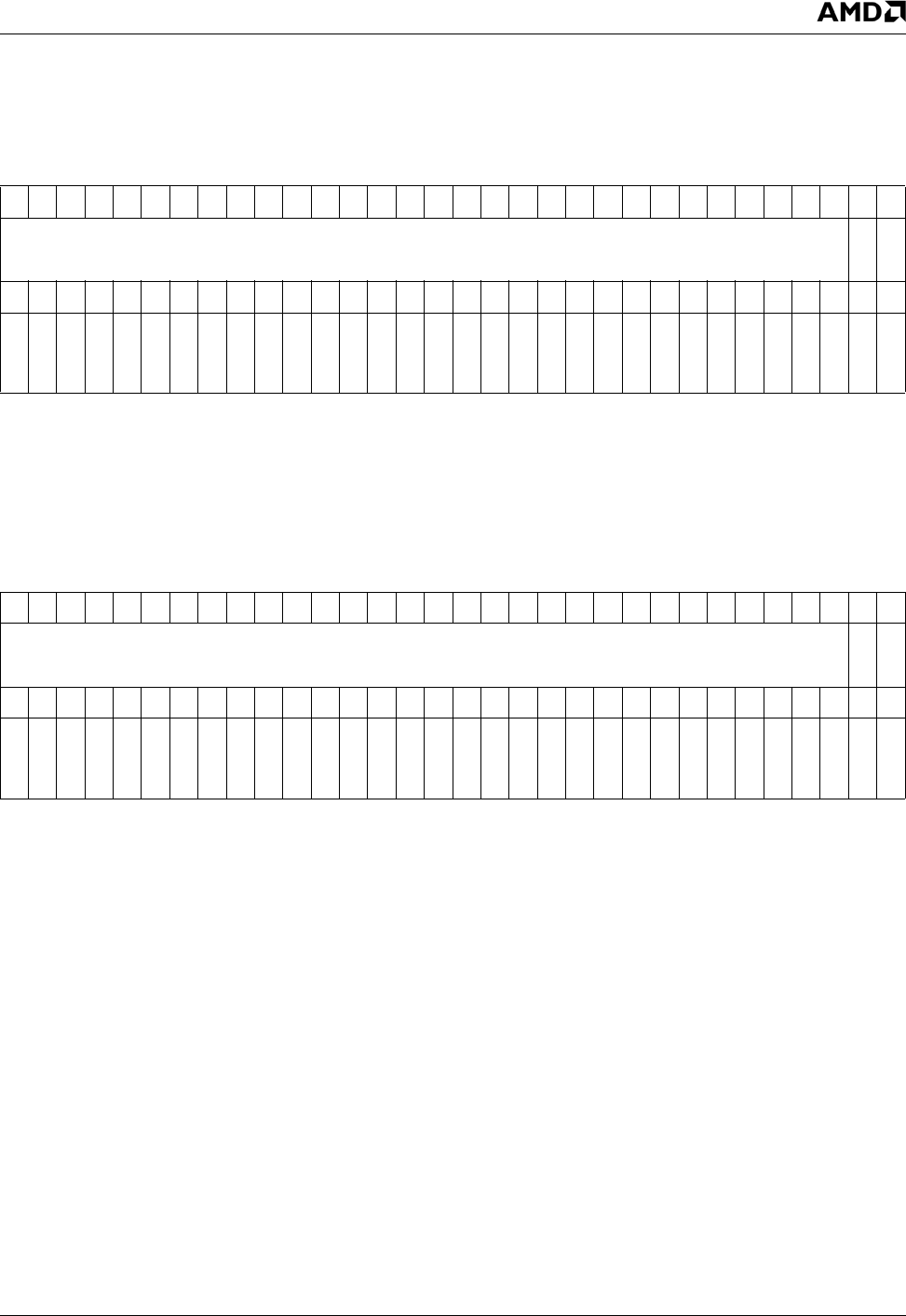

6.14.2.12 GLCP Clock Active Mask for Suspend Acknowledge (GLCP_CLK4ACK)

See "GLCP_CLKOFF Bit Descriptions" on page 551 for bit descriptions.

MSR Address 4C000012h

Typ e R /W

Reset Value 00000000_00000000h

GLCP_CLKDISABLE Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

VIPVIP

VIPGLIU

313029282726252423222120191817161514131211109876543210

AES

AESGLIU

AESEE

GLCPDBG

GLCPGLIU

GLCPPCI

VPVOP

VPDOT_2

VPDOT_1

VPDOT_0

VPGLIU_1

VPGLIU_0

PCIPCIF

PCIPCI

PCIGLIU

GLIU1_1

GLIU1_0

DCGLIU_1

DCGLIU_0

RSVD

DCDOT_0

GLIU0_1

GLIU0_0

GP

GLMC

DRAM

BC_GLIU

BC_VA

MSS

IPIPE

FPUFAST

FPUSLOW

MSR Address 4C000013h

Typ e R /W

Reset Value 00000000_00000000h

GLCP_CLK4ACK Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

VIPVIP

VIPGLIU

313029282726252423222120191817161514131211109876543210

AES

AESGLIU

AESEE

GLCPDBG

GLCPGLIU

GLCPPCI

VPVOP

VPDOT_2

VPDOT_1

VPDOT_0

VPGLIU_1

VPGLIU_0

PCIPCIF

PCIPCI

PCIGLIU

GLIU1_1

GLIU1_0

DCGLIU_1

DCGLIU_0

RSVD

DCDOT_0

GLIU0_1

GLIU0_0

GP

GLMC

DRAM

BC_GLIU

BC_VA

MSS

IPIPE

FPUFAST

FPUSLOW