AMD Geode™ LX Processors Data Book 201

CPU Core Register Descriptions

33234H

5.5.2.112 Memory Subsystem Array Control 1 MSR (MSS_ARRAY_CTL1_MSR)

5.5.2.113 Memory Subsystem Array Control 2 MSR (MSS_ARRAY_CTL2_MSR)

L2 delay control settings.

MSR Address 00001982h

Typ e R /W

Reset Value 00000000_104823CFh

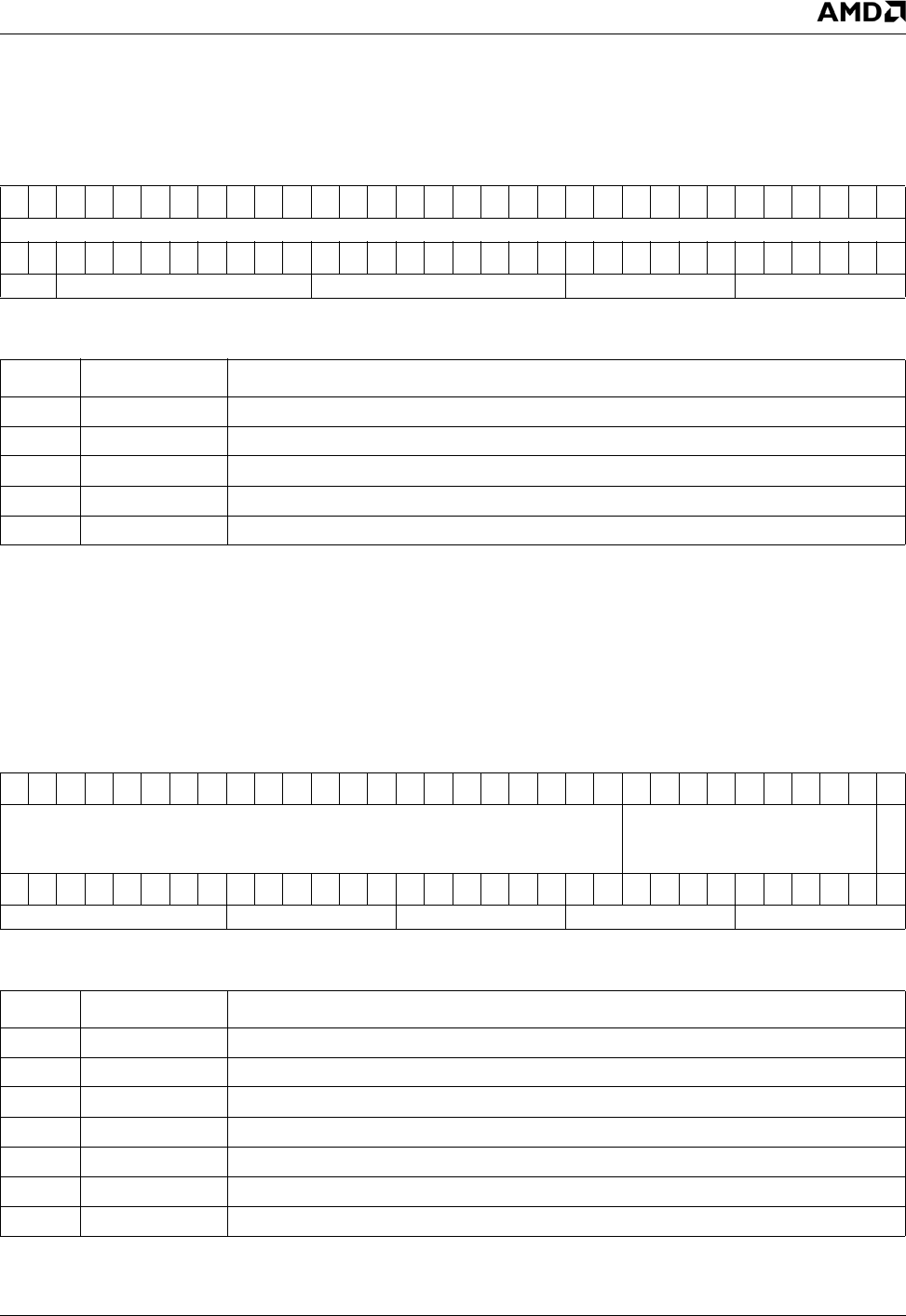

MSS_ARRAY_CTL1_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

RSVD IMDATA1 IMDATA0 IMTAG1 IMTAG0

MSS_ARRAY_CTL1_MSR Bit Descriptions

Bit

Name Description

63:30 RSVD Reserved. (Default = 0)

29:21 IMDATA1 Instruction Memory Subsystem Data 1 Delay Control. (Default = 82)

20:12 IMDATA0 Instruction Memory Subsystem Data 0 Delay Control. (Default = 82)

11:6 IMTAG1 Instruction Memory Subsystem Tag 1 Delay Control. (Default = F)

5:0 IMTAG0 Instruction Memory Subsystem Tag 0 Delay Control. (Default = F)

MSR Address 00001983h

Typ e R /W

Reset Value 00000104_820C30C3h

MSS_ARRAY_CTL2_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD L2DATA1

L2DATA0

313029282726252423222120191817161514131211109876543210

L2DATA0 L2TAG3 L2TAG2 L2TAG1 L2TAG0

MSS_ARRAY_CTL2_MSR Bit Descriptions

Bit Name Description

63:42 RSVD Reserved. (Default = 0)

41:33 L2DATA1 L2 Cache Data 1 Delay Setting. (Default = 82)

32:24 L2DATA0 L2 Cache Data 0 Delay Setting. (Default = 82)

23:18 L2TAG3 L2 Cache Tag 3 Delay Setting. (Default = 3)

17:12 L2TAG2 L2 Cache Tag 2 Delay Setting. (Default = 3)

11:6 L2TAG1 L2 Cache Tag 1 Delay Setting. (Default = 3)

5:0 L2TAG0 L2 Cache Tag 0 Delay Setting. (Default = 3)