AMD Geode™ LX Processors Data Book 595

GeodeLink™ PCI Bridge Register Descriptions

33234H

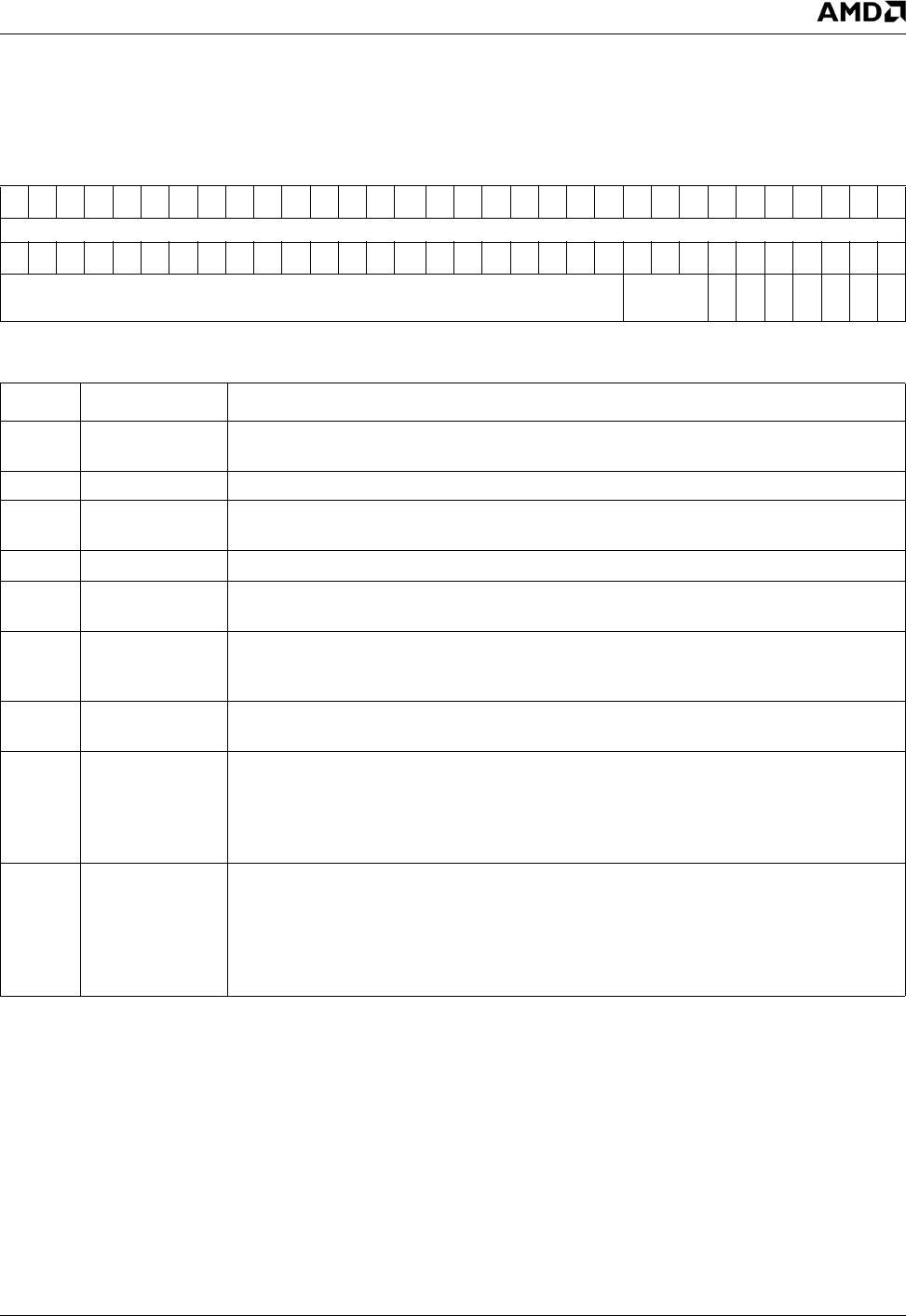

6.16.2.16 GLPCI Spare

MSR Address 5000201Fh

Typ e R /W

Reset Value 00000000_00000003h

GLPCI Spare

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

Spare

313029282726252423222120191817161514131211109876543210

Spare RSVD

AILTO

PPD

PPC

MPC

MME

NSE

SUPO

GLPCI Spare Bit Descriptions

Bit Name Description

63:10 Spare Spare Bits. Extra bits available for future use. These bits may be set and cleared, but do

not control anything.

9:7 RSVD Reserved. Write as read.

6AILTO Alternate Initial Latency Timeout. Enables alternate initial latency timeout values to be

configured via ILTO (MSR 50002010h[41:40]).

5 PPD Post PIO Data. Enables posting of I/O writes to addresses: 170h and 1F0h.

4 PPC Post PIO Control. Enables posting of I/O writes to addresses: 171h, 172h, 173h, 174h,

175h, 176h, 177h, 1F1h, 1F2h, 1F3h, 1F4h, 1F5h, 1F6h and 1F7h.

3MPC Maximum Posted Count. Controls the maximum number of PIO I/O writes that may be

posted in the GLPCI. When cleared, one I/O write may be posted. When set, two I/O

writes may be posted.

2MME Mask External MSR Exceptions. Set to 1 to force the GLIU synchronous exception flag

to be cleared for all external MSR transactions.

1NSE No Synchronous Exceptions. Controls when out-bound read data is written into the

OBRD FIFO. When this bit is cleared. the GLPCI pipelines the writing of all out-bound

read data into the FIFO. This allows PCI transaction status to be sampled and included

synchronously with the read data. When this bit is cleared, the GLPCI only pipelines read

data for external MSR accesses and I/O read of the configuration data port (0CFCh).

0SUPO Strict Up-Stream Ordering. Controls how out-bound reads get sorted with in-bound

writes. When this bit is set the ordering rules are strictly applied; meaning that all GLIU

write responses associated with a in-bound PCI write transaction must complete before

data from a subsequent out-bound PCI read may be placed onto the GLIU. When this bit

is cleared the out-bound read data may be placed onto the GLIU after the in-bound write

data has been placed onto the GLIU.