AMD Geode™ LX Processors Data Book 345

Display Controller Register Descriptions

33234H

6.6.11.2 DC VBI Odd Control (DC_VBI_ODD_CTL)

Settings written to this register do not take effect until the start of the following frame or interlaced field.

6.6.11.3 DC VBI Horizontal Control (DC_VBI_HOR)

Settings written to this register do not take effect until the start of the following frame or interlaced field.

28 VBI_ENA VBI Enable. Setting this bit to 1 enables VBI (Vertical Blank Interrupt) data. This is a data

stream that is placed in the off-screen region at the start of each field. This data is passed

through the graphics output path, but is not filtered or modified in any way.

27:0 VBI_EVEN_

OFFSET

VBI Even Address Offset. Indicates the starting offset for VBI data for even fields. This

address must be QWORD aligned; the low three bits are always 0. If interlacing is dis-

abled, this offset is used for VBI data.

DC Memory Offset 0A4h

Typ e R /W

Reset Value xxxxxxxxh

DC_VBI_EVEN_CTL Bit Descriptions (Continued)

Bit Name Description

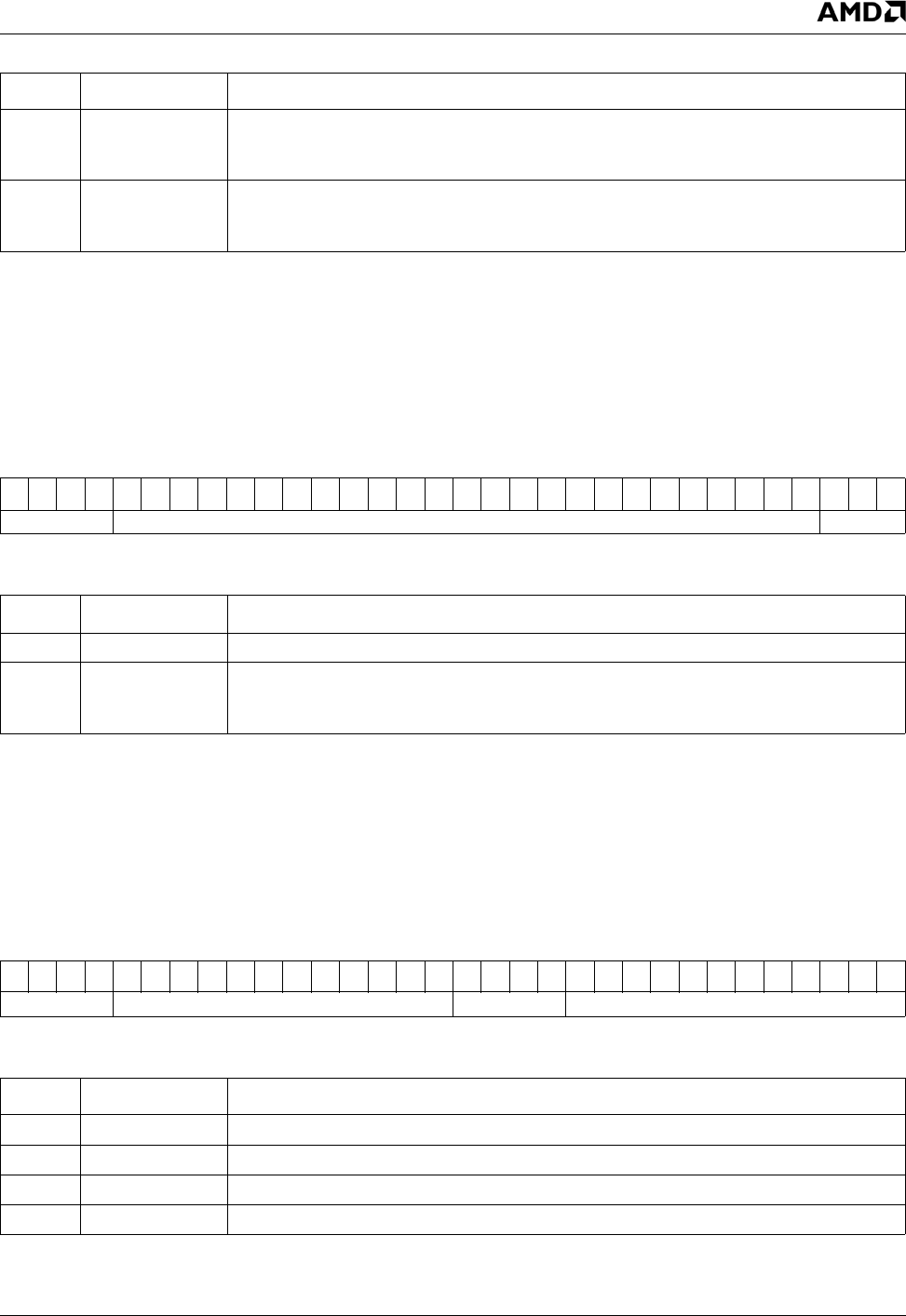

DC_VBI_ODD_CTL Register Map

313029282726252423222120191817161514131211109876543210

RSVD VBI_ODD_OFFSET 0

DC_VBI_ODD_CTL Bit Descriptions

Bit Name Description

31:28 RSVD Reserved. Set to 0.

27:0 VBI_ODD_

OFFSET

VBI Odd Address Offset. Indicates the starting offset for VBI data for odd fields. This

address must be QWORD aligned; the low three bits are always 0. If interlacing is dis-

abled, the even offset is used for VBI data.

DC Memory Offset 0A8h

Typ e R /W

Reset Value xxxxxxxxh

DC_VBI_HOR Register Map

313029282726252423222120191817161514131211109876543210

RSVD VBI_H_END RSVD VBI_H_START

DC_VBI_HOR Bit Descriptions

Bit Name Description

31:28 RSVD Reserved. Set to 0.

27:16 VBI_H_END VBI Horizontal End. Specifies the horizontal end position for VBI data minus 1 pixel.

15:12 RSVD Reserved. Set to 0.

11:0 VBI_H_START VBI Horizontal Start. Specifies the horizontal start position for VBI data minus 1 pixel.