AMD Geode™ LX Processors Data Book 659

Instruction Set

33234H

windex 1 (imm8) The range given by [index1 (imm8) + 15: index1 (imm8)].

windex 2 (imm8) The range given by [index2 (imm8) + 15: index2 (imm8)].

windex 3 (imm8) The range given by [index3 (imm8) r15: indes3 (imm8)].

windexall (imm8) The four different index # (imm8) ordered in the same way as word.

msb [bytes] The most significant bits of the different eight bytes in QWORD, ordered from higher to lower

bytes.

msb [words] The most significant bits (sign bit) of the different four WORDs in a QWORD ordered from higher

to lower.

trun If required, the resultant data is truncated to remain within the associated range.

n Stack register number.

TOS (Note 1) Top of stack register pointed to by SSS in the status register.

ST(1) (Note 1) FPU register next to TOS.

ST(n) (Note 1) A specific FPU register, relative to TOS.

M.WI 16-bit integer operand from memory.

M.SI 32-bit integer operand from memory.

M.LI 64-bit integer operand from memory.

M.SR 32-bit real operand from memory.

M.DR 64-bit real operand from memory.

M.XR 80-bit real operand from memory.

M.BCD 18-digit BCD integer operand from memory.

CC FPU condition code.

Env Regs Status, Mode Control and Tag registers, Instruction Pointer and Operand Pointer.

Note 1. All references to TOS and ST(n) refer to stack layout prior to execution. Values popped off the stack are discarded.

A POP from the stack increments the top of the stack pointer. A PUSH to the stack decrements the top of the stack

pointer.

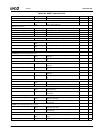

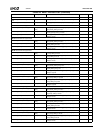

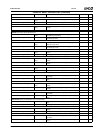

Table 8-27. MMX™, FPU, and AMD 3DNow!™ Instruction Set Table Legend

Abbreviation Description