AMD Geode™ LX Processors Data Book 583

GeodeLink™ PCI Bridge Register Descriptions

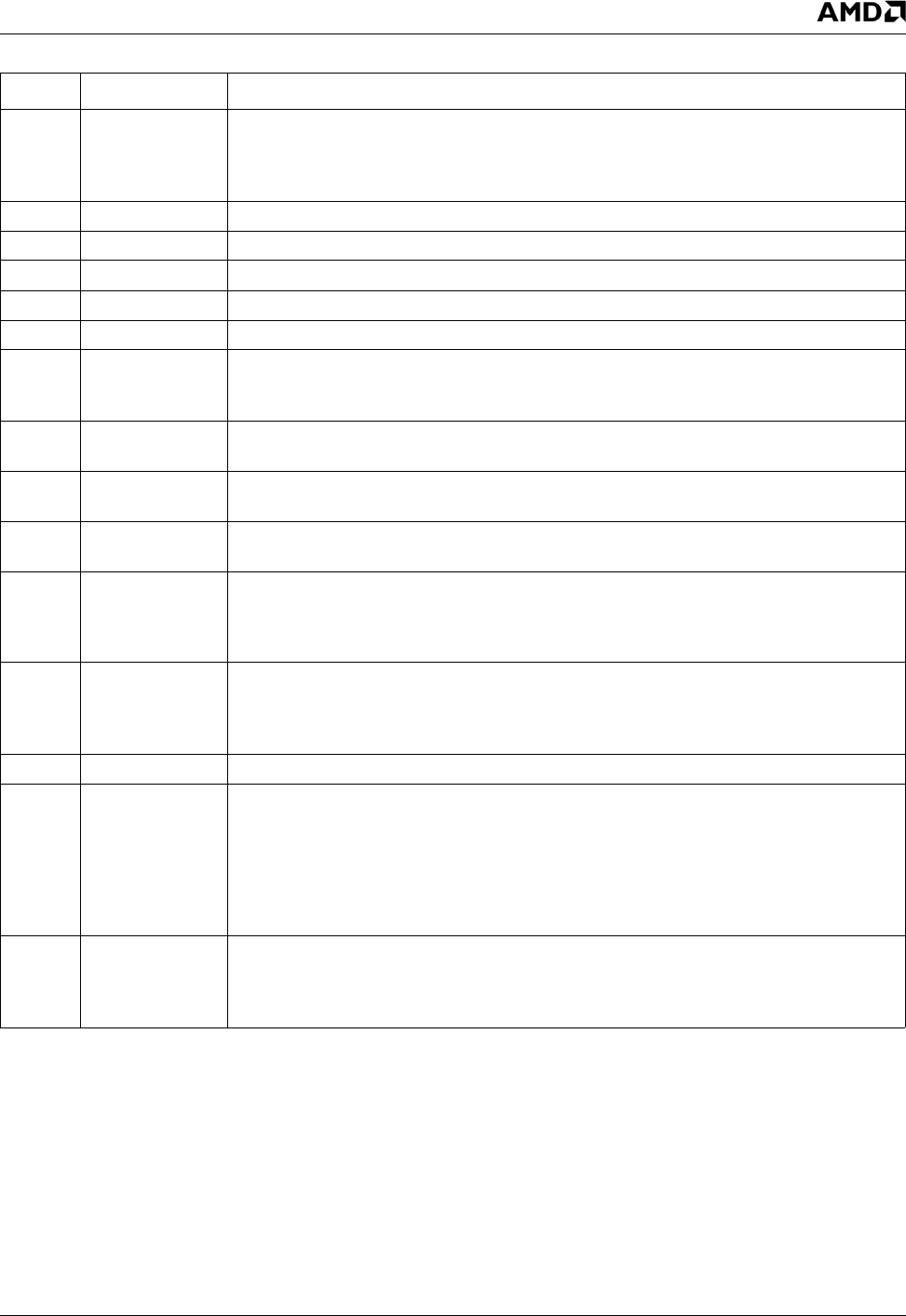

33234H

20 OV0 Override 0. Enables requester0 to override the repeat-count and grant-hold for other

requestors. When OV0 is set and REQ0# is asserted, repeat-count and grant-hold mech-

anisms for other masters are temporarily disabled. This bit does not change the round

robin arbitration cycle, it only overrides repeat-count and grant-hold for other requestors.

19 RSVD (RO) Reserved (Read Only). Reserved for future use.

18 MSK2 Request Mask 2. Disables REQ2# when set to 1. Resets to 0.

17 MSK1 Request Mask 1. Disables REQ1# when set to 1. Resets to 0.

16 MSK0 Request Mask 0. Disables REQ0# when set to 1. Resets to 0.

15:12 RSVD (RO) Reserved (Read Only). Reserved for future use.

11 CPRE CPU Preemption Enable. When set to 1, the CPU’s PCI grant may be de-asserted

before the CPU’s request is de-asserted. If this bit is cleared, the arbiter ignores CH and

CR, bits [47:44] and [63:60].

10 PRE2 Preemption Enable 2. When set to 1, GNT2# may be de-asserted before REQ2# is de-

asserted. If this bit is cleared, the arbiter ignores R2 and H2, bits [59:56] and [43:40].

9PRE1 Preemption Enable 1. When set to 1, GNT1# may be de-asserted before REQ1# is de-

asserted. If this bit is cleared, the arbiter ignores the R1 and H1, bits [55:52] and [39:36].

8PRE0 Preemption Enable 0. When set to 1, GNT0# may be de-asserted before REQ0# is de-

asserted. If this bit is cleared, the arbiter ignores R0 and H0, bits [51:48] and [35:32].

7 BM1 (RO) Broken Master 1 (Read Only). Indicates when a broken master is attached to REQ1#.

This bit is set when the arbiter detects that the PCI bus master attached to REQ1# has

not asserted FRAME# within 16 PCI clock edges after being granted the PCI bus. This bit

is cleared by setting BMD (bit 1) to 1.

6 BM0 (RO) Broken Master 0 (Read Only). Indicates when a broken master is attached to REQ0#.

This bit is set when the arbiter detects that the PCI bus master attached to REQ[0]# has

not asserted FRAME# within 16 PCI clock edges after being granted the PCI bus. This bit

is cleared by setting the BMD (bit 1) to 1.

5:2 RSVD (RO) Reserved (Read Only). Reserved for future use.

1BMD Broken Master Timer Disable. Controls the operation of the broken master detector in

the PCI arbiter. When set to 1, the arbiter does not recognize a broken master condition

on the PCI bus. When cleared to 0, the arbiter detects a broken master condition when a

granted PCI bus master takes 16 or more clock cycles before asserting FRAME#. The

broken master is NOT allowed to gain access to the PCI bus. Software may restore any

broken master’s permission to use the PCI bus by clearing this bit, and optionally, setting

it again.

0PARK Parking Policy. When cleared to 0, the arbiter always parks the PCI bus on the

AMD Geode™ LX processor. When set to 1, the arbiter parks the PCI bus on the last

granted bus master. If this bit is set, the clock for the PCI-fast clock domain should not be

gated.

GLPCI_ARB Bit Definitions (Continued)

Bit Name Description