AMD Geode™ LX Processors Data Book 591

GeodeLink™ PCI Bridge Register Descriptions

33234H

6.16.2.12 GLCPI Memory Region 3 Configuration (GLPCI_R3)

MSR Address 5000201Bh

Typ e R /W

Reset Value 00000000_00000000h

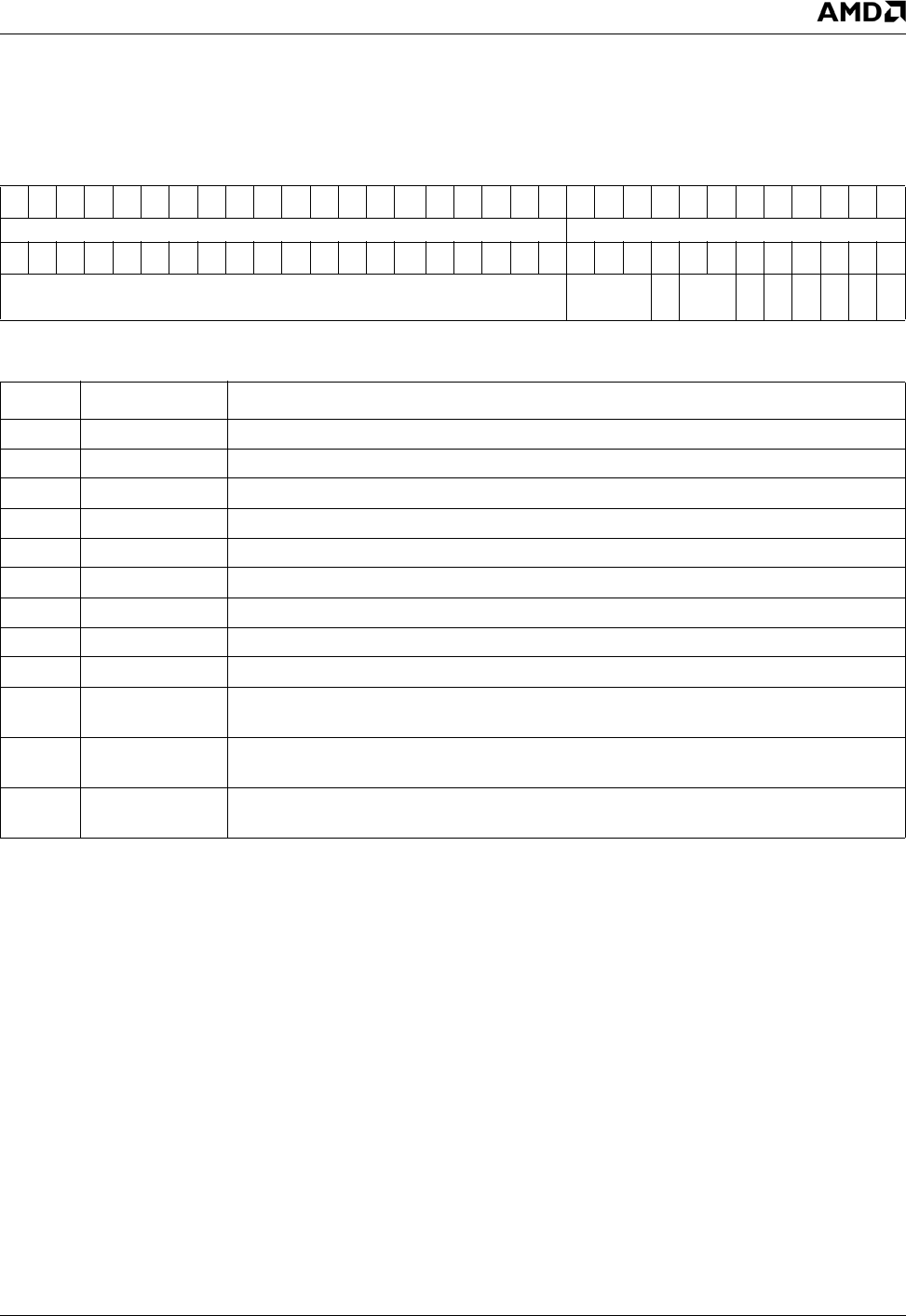

GLPCI_R3 Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

TOP RSVD

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

BASE RSVD

EN

RSVD

PF

WC

RSVD

WP

DD

CD

GLPCI_R3 Bit Descriptions

Bit Name Description

63:44 TOP Top of Region. 4 KB granularity, inclusive.

43:32 RSVD (RO) Reserved (Read Only). Reserved for future use.

31:12 BASE Base of Region. 4 KB granularity, inclusive.

11:9 RSVD (RO) Reserved (Read Only). Reserved for future use.

8EN Region Enable. Set to 1 to enable access to this region.

7:6 RSVD (RO) Reserved (Read Only). Reserved for future use.

5PF Prefetchable. Reads to this region have no side-effects.

4WC Write Combine. Writes to this region may be combined.

3 RSVD (RO) Reserved (Read Only). Reserved for future use.

2WP Write Protect. When set to 1, only read accesses are allowed. Write accesses are

ignored (master abort).

1DD Discard Data. When set to 1, write access are accepted and discarded. Read accesses

are ignored (master abort).

0CD Cache Disable. When set to 1, accesses are marked as non-coherent. When cleared to

0, accesses are marked as coherent.