452 AMD Geode™ LX Processors Data Book

Video Processor Register Descriptions

33234H

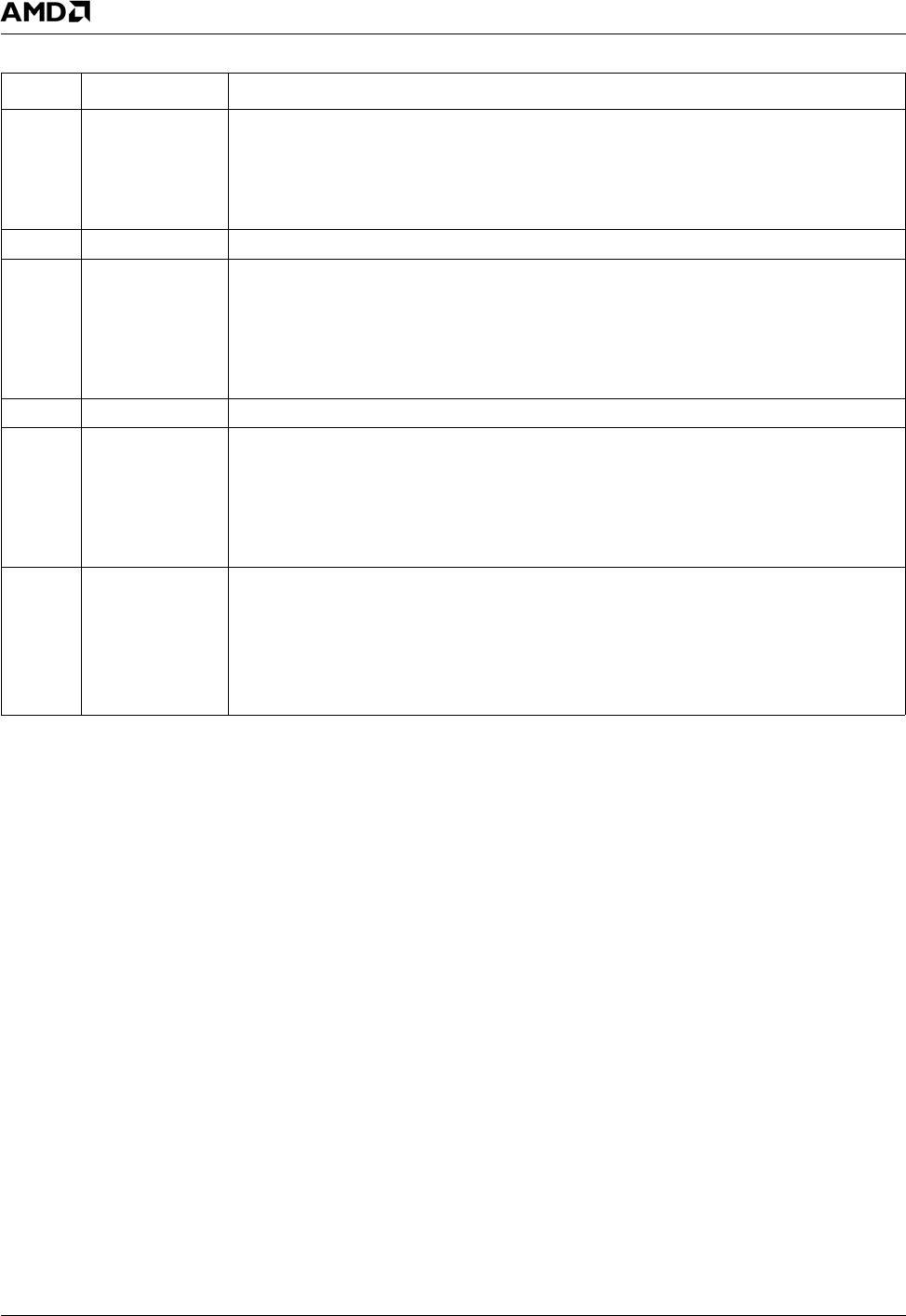

29 FP_HSYNC_

POL

FP_HSYNC Input Polarity. Selects positive or negative polarity of the FP_HSYNC input.

Program this bit to match the polarity of the incoming FP_HSYNC signal. Note that FP

Memory Offset 408h[22] controls the polarity of the output HSYNC.

0: FP_HSYNC is normally low, transitioning high during sync interval. (Default)

1: FP_HSYNC is normally high, transitioning low during sync interval

28 RSVD Reserved. This bit is not defined.

27 HSYNC_SRC TFT Horizontal Sync Source. Selects a delayed or undelayed TFT horizontal sync out-

put. This bit determines whether to use the HSYNC for the TFT panel without delaying

the input HSYNC, or delay the HSYNC before sending it on to TFT. HSYNC_DELAY

(bits [7:5]) determine the amount of the delay.

0: Do not delay the input HSYNC before it is output onto the LP/HSYNC. (Default)

1: Delay the input HSYNC before it is output onto the LP/HSYNC

26:8 RSVD Reserved. R/W; no function.

7:5 HSYNC_DELAY Horizontal Sync Delay. Selects the amount of delay in the output HSYNC pulse with

respect to the input HSYNC pulse. The delay is programmable in steps of one DOTCLK.

SYNC_SRC (bit 27) must be set in order for HSYNC_DELAY to be recognized.

HSYNC_DELAY is only used for TFT modes.

000: No delay from the input HSYNC. (Default)

001-111: Delay the HSYNC start by one to seven DOTCLKs.

4:0 HSYNC_PLS_

WIDTH

Horizontal Sync Pulse Width. Stretch the HSYNC pulse width by up to 31 DOTCLKs.

The pulse width is programmable in steps of one DOTCLK. HSYNC_PLS_WIDTH is only

used for TFT modes.

00000: Does not generate the HSYNC pulse. The TFT panel uses the default input tim-

ing, which is selected by keeping the HSYNC_SRC bit (bit 27) set to 0. (Default)

00001-11111: The HSYNC pulse width can be varied from one to 31 DOTCLKs.

PT1 Bit Descriptions (Continued)

Bit Name Description