AMD Geode™ LX Processors Data Book 485

Video Input Port Register Descriptions

33234H

6.10.1.3 GLD SMI MSR (GLD_MSR_SMI)

MSR Address 54002002h

Typ e R /W

Reset Value 000000000_ xxxx7FFFh

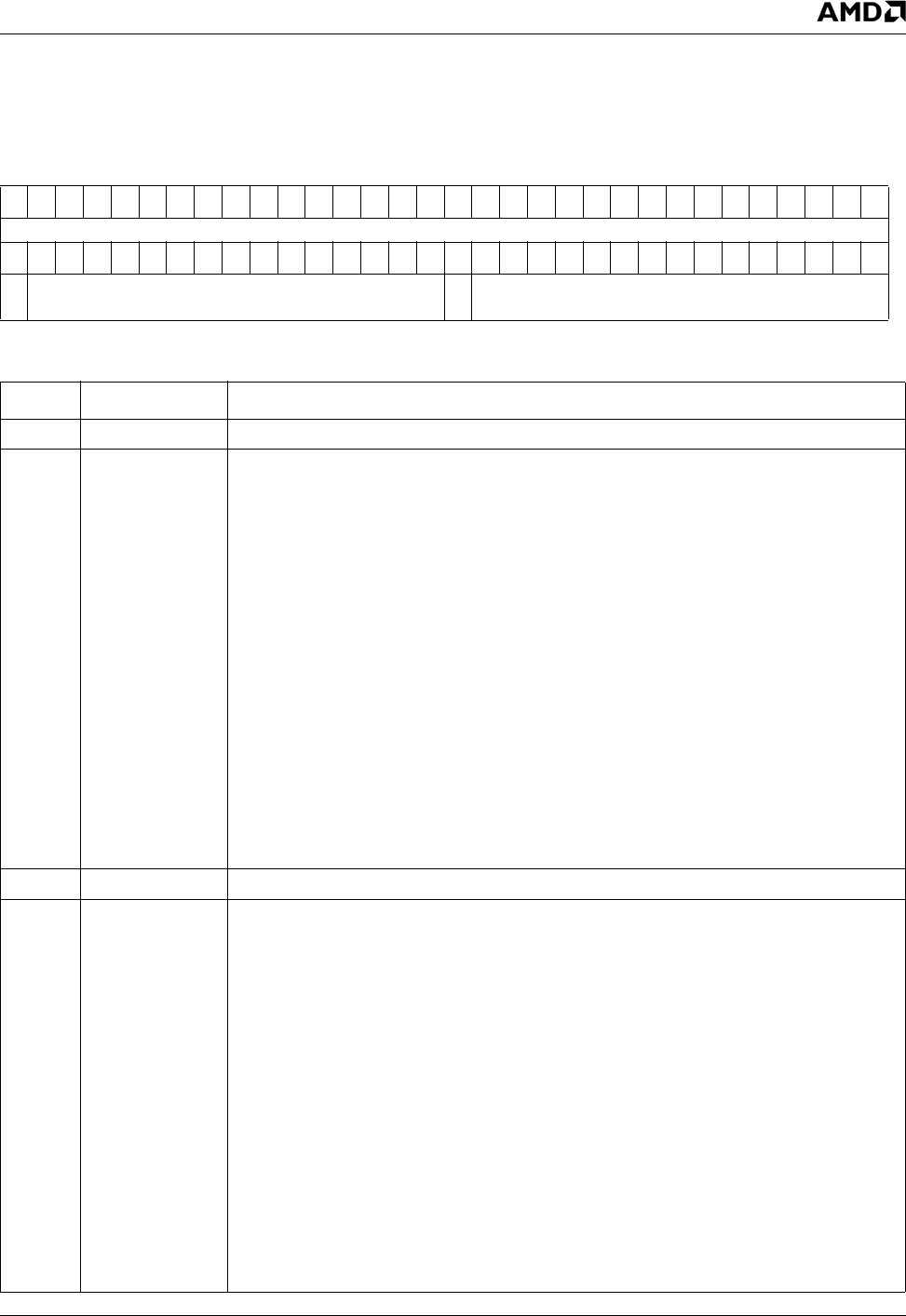

GLD_MSR_SMI Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD

SMI_STATUS

RSVD

SMI_MASK

GLD_MSR_SMI Bit Descriptions

Bit Name Description

63:31 RSVD Reserved.

30:16 SMI_STATUS VIP SMI Interrupt Status.

0: SMI not pending.

1: SMI pending.

Writing a 1 to this bit clears the status:

Bit 30: Reserved.

Bit 29: FIFO overflow error.

Bit 28: FIFO threshold hit.

Bit 27: Long line (> 3000 clocks) error.

Bit 26: Vertical timing error.

Bit 25: Active pixels per line error.

Bit 24: VIP clock input error.

Bit 23: Ancillary packet checksum error.

Bit 22: Message buffer full or ancillary threshold packet count reached.

Bit 21: End of vertical blanking.

Bit 20: Start of vertical blanking.

Bit 19: Start of even field.

Bit 18: Start of odd field.

Bit 17: Current line = VIP Line Target (see Current/Target Line register).

Bit 16: GLIU Address or Type error.

15 RSVD Reserved.

14:0 SMI_MASK VIP SMI Masks.

0: Enable, unmask the SMI.

1: Disabled, mask the SMI.

Bit 14: Reserved.

Bit 13: FIFO overflow error.

Bit 12: FIFO threshold hit.

Bit 11: Long line (> 3000 clocks) error.

Bit 10: Vertical timing error.

Bit 9: Active pixels per line error.

Bit 8: VIP clock input error.

Bit 7: Ancillary packet checksum error.

Bit 6: Message buffer full or ancillary threshold packet count reached.

Bit 5: End of vertical blanking.

Bit 4: Start of vertical blanking.

Bit 3: Start of even field.

Bit 2: Start of odd field.

Bit 1: Current line = VIP Line Target (see Current/Target Line register).

Bit 0: GLIU Address or Type error.