AMD Geode™ LX Processors Data Book 41

Signal Definitions

33234H

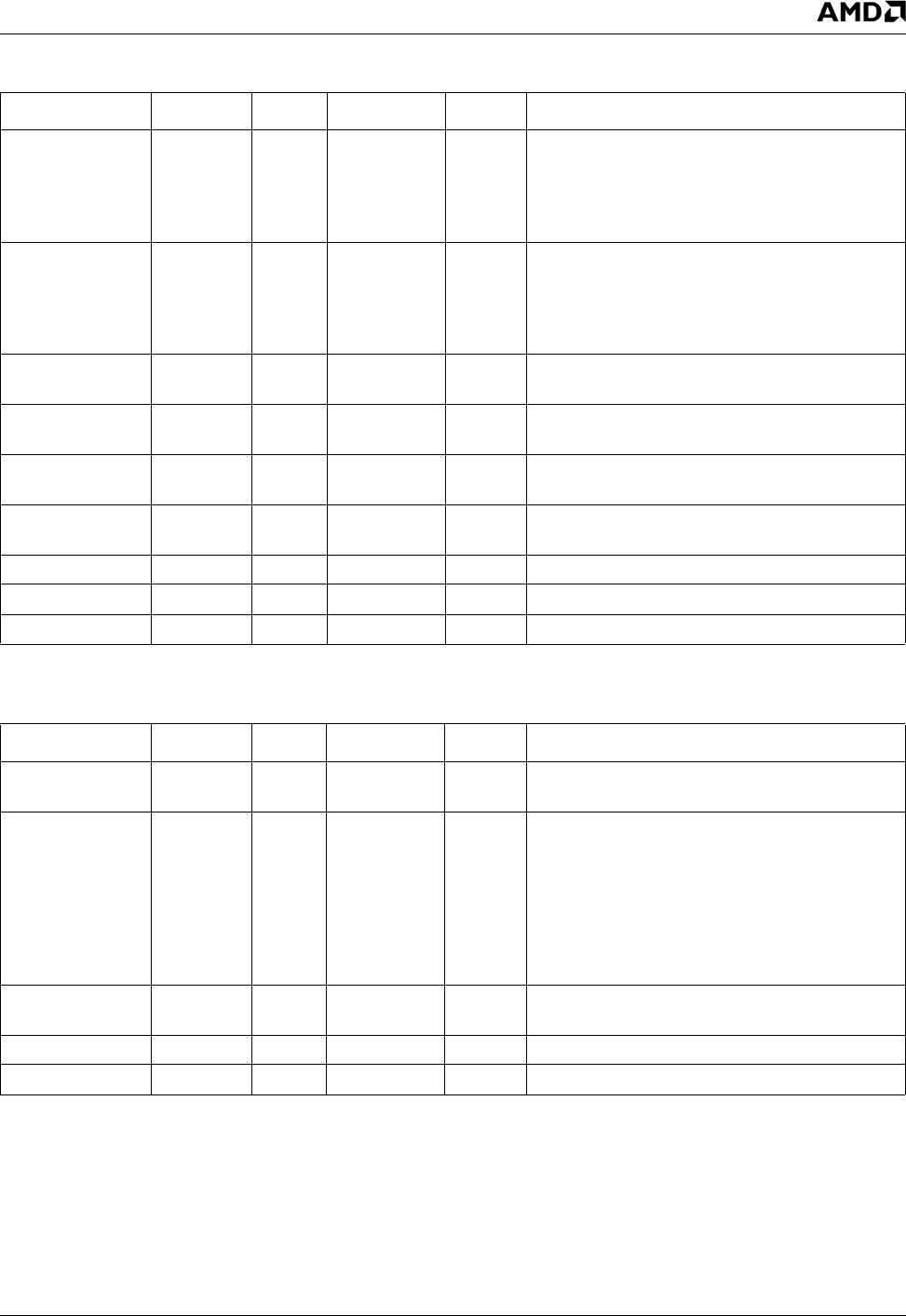

3.4.7 CRT Display Interface Signals

Signal Name Ball No. Type f V Description

HSYNC AE3 I/O 0-350 Mb/s 3.3

(5vt)

Horizontal Sync. Horizontal Sync establishes

the line rate and horizontal retrace interval for an

attached CRT. The polarity is programmable

(See Section 6.8.3.2 on page 422, VP Memory

Offset 008h[8]).

VSYNC AD3 I/O 0-350 Mb/s 3.3

(5vt)

Vertical Sync. Vertical Sync establishes the

screen refresh rate and vertical retrace interval

for an attached CRT. The polarity is programma-

ble (See Section 6.8.3.2 on page 422, VP Mem-

ory Offset 008h[9]).

DVREF W1 A Analog 1.235 Video DAC Voltage Reference. Connect this

pin to a 1.235V voltage reference.

DRSET Y1 A Analog N/A DAC Current Setting Resistor. 1.21K, 1% to

DAV

SS

.

DAV

DD

[3:0] W4, V4,

V1, U1

APWR Analog 3.3 DAC Analog Power Connection.

DAV

SS

[3:0] W2, Y2,

V3, U3

AGND Analog 0 DAC Analog Ground Connection.

RED W3 A Analog N/A Red DAC Output. Red analog output.

GREEN V2 A Analog N/A Green DAC Output. Green analog output.

BLUE U2 A Analog N/A Blue DAC Output. Blue analog output.

3.4.8 VIP Interface Signals

Signal Name Ball No. Type f V Description

VIPCLK AL12 I/O

(PD)

0-75 MHz 3.3 Video Input Port Clock.

VID[7:0] AK12,

AL13,

AK13,

AJ13,

AH13,

AL15,

AK15,

AJ15

I/O

(PD)

0-150 Mb/s 3.3 Video Input Port Data.

VIPSYNC AL14 I/O

(PD)

0-150 Mb/s 3.3 Video Input Port Sync Signal.

VIP_HSYNC AE2 I 0-150 Mb/s 3.3 Video Input Port Horizontal Sync.

VIP_VSYNC AD4 I 0-150 Mb/s 3.3 Video Input Port Vertical Sync.