182 AMD Geode™ LX Processors Data Book

CPU Core Register Descriptions

33234H

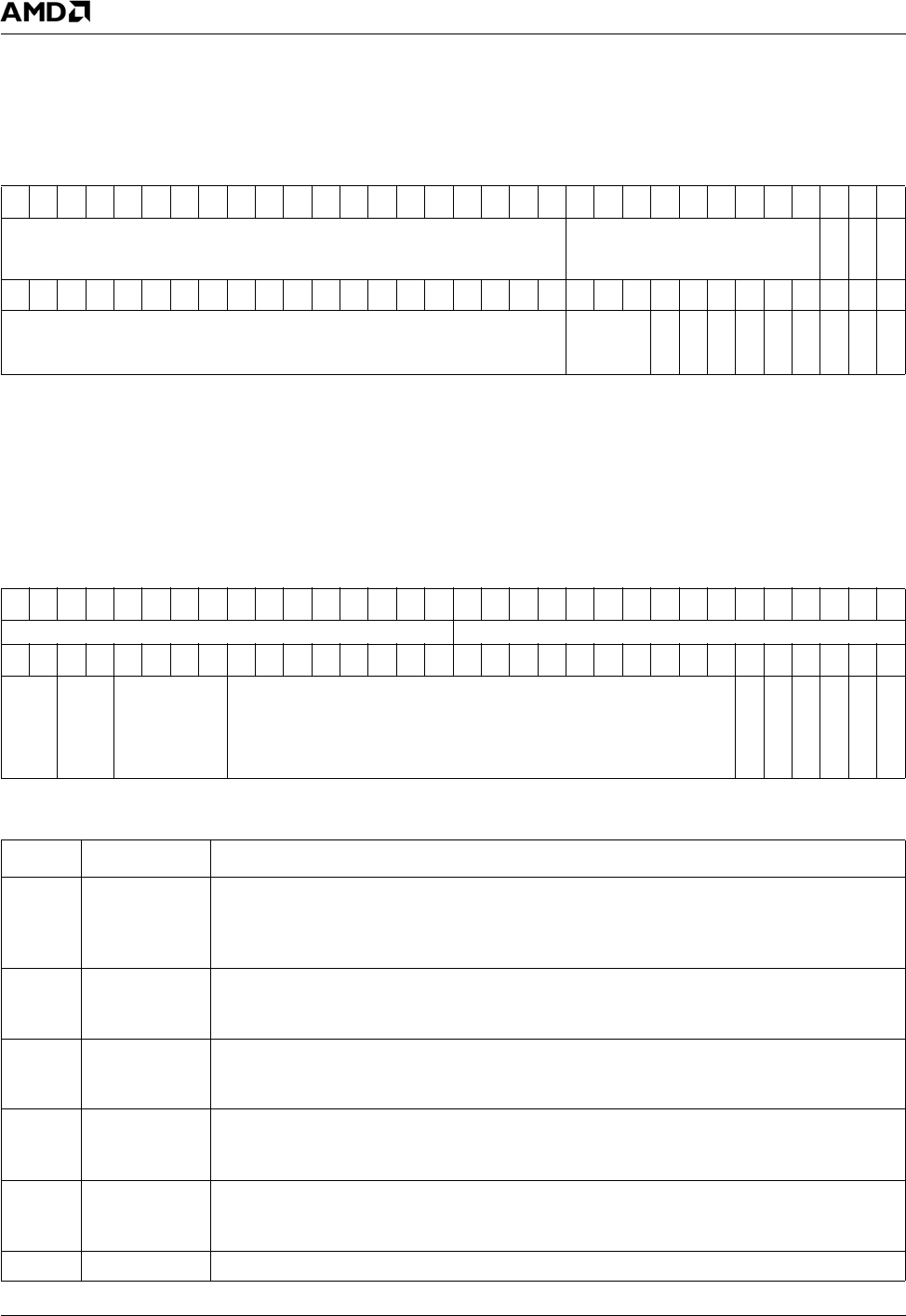

5.5.2.87 L2 TLB/DTE/PTE Entry with Increment MSR (L2TLB_ENTRY_I_MSR)

Bit descriptions for this register are the same as for MSR 0000189Eh, except read/write of this register causes an auto-

increment on the L2TLB_INDEX_MSR (MSR 0000189Ch).

5.5.2.88 Data Memory Subsystem Built-In Self-Test MSR (DM_BIST_MSR)

MSR Address 0000189Fh

Typ e R /W

Reset Value 00000000_00000000h

L2TLB_ENTRY_I_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

LINADDR RSVD

WP

WA_WS

WC

313029282726252423222120191817161514131211109876543210

PHYSADDR RSVD

GLOBAL

RSVD

DIRTY

ACC

CD

WT_BR

US

WR

VALID

MSR Address 000018C0h

Typ e R /W

Reset Value 00000000_00000000h

DM_BIST_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

TAG CMP TAGDAT

313029282726252423222120191817161514131211109876543210

TLBCMP

TLBDAT

DATA RSVD

RETEN_TLB

RUN_TLB

RETEN_DATA

RUN_DATA

RETEN_TAG

RUN_TAG

DM_BIST_MSR Bit Descriptions

Bits Name Description

63:48 TAGCMP[15:0]

(RO)

Cache Tag Comparators (Read Only). BIST results for cache tag comparators

(array15...array0).

0: Fail.

1: Pass.

47:32 TAGDAT[15:0]

(RO)

Cache Tag Data (Read Only). BIST results for cache tag data integrity (array15...array0).

0: Fail.

1: Pass.

31:30 TLBCMP[1:0]

(RO)

L2 TLB Comparators (Read Only). BIST results for L2 TLB comparators (array1, array0).

0: Fail.

1: Pass.

29:28 TLBDAT[1:0]

(RO)

L2 TLB Data (Read Only). BIST results for L2 TLB data integrity (array1, array0).

0: Fail.

1: Pass.

27:24 DATA[3:0] (RO) Data Cache Data (Read Only). BIST results for data cache data arrays[3:0].

0: Fail.

1: Pass.

23:6 RSVD (RO) Reserved (Read Only). Read as 0.