AMD Geode™ LX Processors Data Book 37

Signal Definitions

33234H

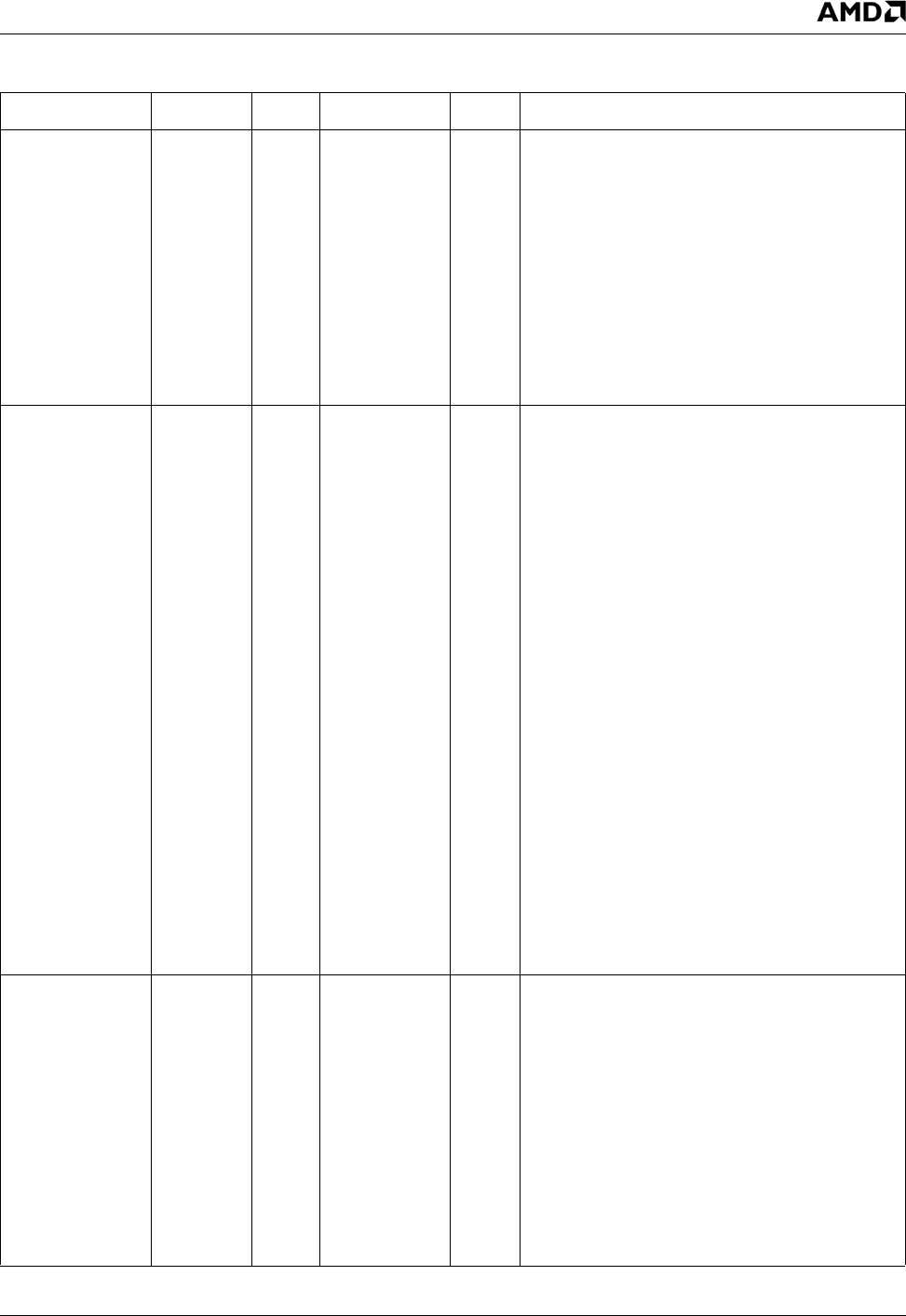

3.4.5 PCI Interface Signals

Signal Name Ball No. Type f V Description

AD[31:0] See Table

3-6 on

page 30

I/O 33-66 Mb/s 3.3 Multiplexed Address and Data. Addresses and

data are multiplexed together on the same pins.

A bus transaction consists of an address phase

in the cycle in which FRAME# is asserted fol-

lowed by one or more data phases. During the

address phase, AD[31:0] contain a physical 32-

bit address. During data phases, AD[7:0] contain

the least significant byte (LSB) and AD[31:24]

contain the most significant byte (MSB). Write

data is stable and valid when IRDY# is asserted

and read data is stable and valid when TRDY# is

asserted. Data is transferred during the SYSREF

when both IRDY# and TRDY# are asserted.

CBE[3:0]# AH31,

AH27,

AL26,

AJ22

I/O 33-66 Mb/s 3.3 Multiplexed Command and Byte Enables. C/

BE# are the bus commands and byte enables.

During the address phase of a transaction when

FRAME# is active, C/BE# define the bus com-

mand. During the data phase C/BE# are used as

byte enables. The byte enables are valid for the

entire data phase and determine which byte

lanes carry meaningful data. C/BE0# applies to

byte 0 (LSB) and C/BE3# applies to byte 3

(MSB). The command encoding and types are

listed below:

0000: Interrupt Acknowledge

0001: Special Cycle

0010: I/O Read

0011: I/O Write

0100: Reserved

0101: Reserved

0110: Memory Read

0111: Memory Write

1000: Reserved

1001: Reserved

1010: Configuration Read

1011: Configuration Write

1100: Memory Read Multiple

1101: Dual Address Cycle (RSVD)

1110: Memory Read Line

1111: Memory Write and Invalidate

PAR AJ27 I/O 33-66 Mb/s 3.3 Parity. PAR is used with AD[31:0] and C/BE# to

generate even parity. Parity generation is

required by all PCI agents: the master drives PAR

for address and write-data phases and the target

drives PAR for read-data phases.

For address phases, PAR is stable and valid one

SYSREF after the address phase.

For data phases, PAR is stable and valid one

SYSREF after either IRDY# is asserted on a

write transaction or after TRDY# is asserted on a

read transaction. Once PAR is valid, it remains

valid until one SYSREF after the completion of

the data phase.