530 AMD Geode™ LX Processors Data Book

Security Block Register Descriptions

33234H

6.12.3.20 SB EEPROM Command (SB_EEPROM_COMM)

SB Memory Offset 800h

Typ e R /W

Reset Value 00000000h

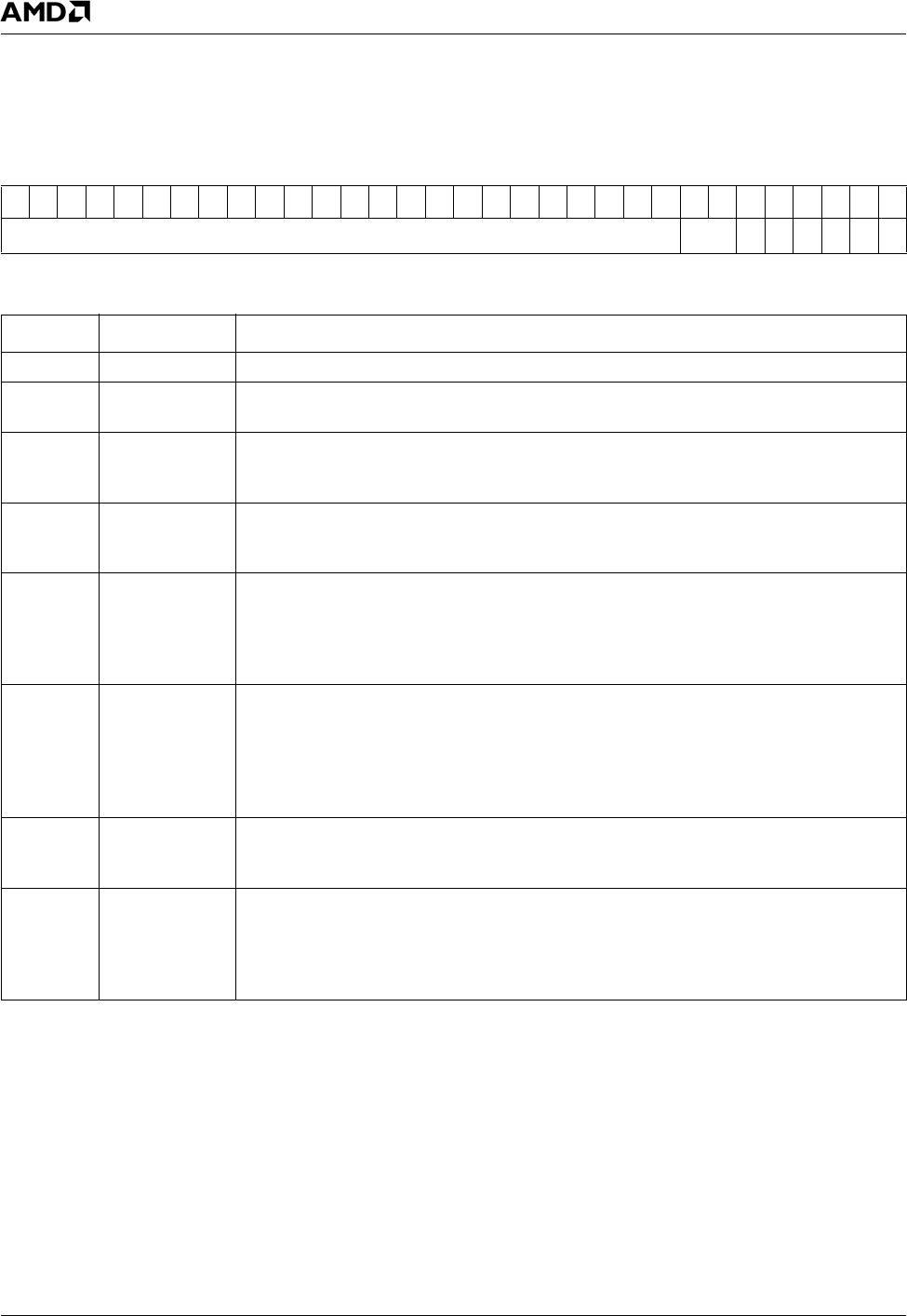

SB_EEPROM_COMM Register Map

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD RSVD

HKD

SL

KV

EX

WR

ST

SB_EEPROM_COMM Bit Descriptions

Bit Name Description

31:8 RSVD Reserved.

7:6 RSVD Reserved. These bits are implemented but reserved for future use. When writing to this

register, software should set these bits to 0 and ignore them on read.

5HKD Hidden Key Disable. Reset to 0. When set, this bit disables the hidden key by forcing

all of the bits to zero. This bit can be written to a 1 by software, but once set, it can only

be cleared by reset. Setting this bit also forces the Key Valid bit (bit 3) to 0.

4SD Soft Lock. Reset to 0. When set, this bit locks the same debug functions locked by the

DBL bit (SB Memory Offset 80Ch[10:8]), and is displayed in the Access Control register.

This bit can be written to a 1 by software, but once set, it can only be cleared by reset.

3KV Key Valid. Reset to 0. After reset, this bit is set automatically by the state machine to

indicate that the automatic load of the hidden key into the AES key register has com-

pleted and the key is now ready for use. No AES operations using the hidden key regis-

ter should be initiated before this bit is set. This bit is cleared by reset or by asserting the

Hidden Key Disable bit (bit 5).

2EX Exception. The current access operation did not complete successfully. Note that this

bit may also be set after a reset if the initial read of the EEPROM control bytes or hidden

key did not complete successfully. This bit should only be set on a fatal hardware access

error. Write 1 to clear. If the exception occurs on the initial EEPROM read after reset, it

is assumed that no EEPROM is preset and the EEPROM interface is disabled. When

the interface is disabled, this bit is not clearable.

1WR Write. When set, the EEPROM interface initiates a write operation to the EEPROM

when the START bit (bit 0) is set. When reset, the EEPROM interface initiates a read

operation when the START bit is set.

0ST START. When set, this bit commands the EEPROM interface to start a new operation

based on the current Control register setting and the settings in the Address and Data

registers. This bit is reset automatically when the operation completes. Setting this bit

also clears the EEPROM Complete flag in the AES Interrupt register (SB Memory Offset

008h[18]) and in the SMI MSR register (MSR 58002002h[34]).