492 AMD Geode™ LX Processors Data Book

Video Input Port Register Descriptions

33234H

6.10.2.3 VIP Status (VIP_STATUS)

VIP Memory Offset 08h

Typ e R /W

Reset Value xxxxxxxxh

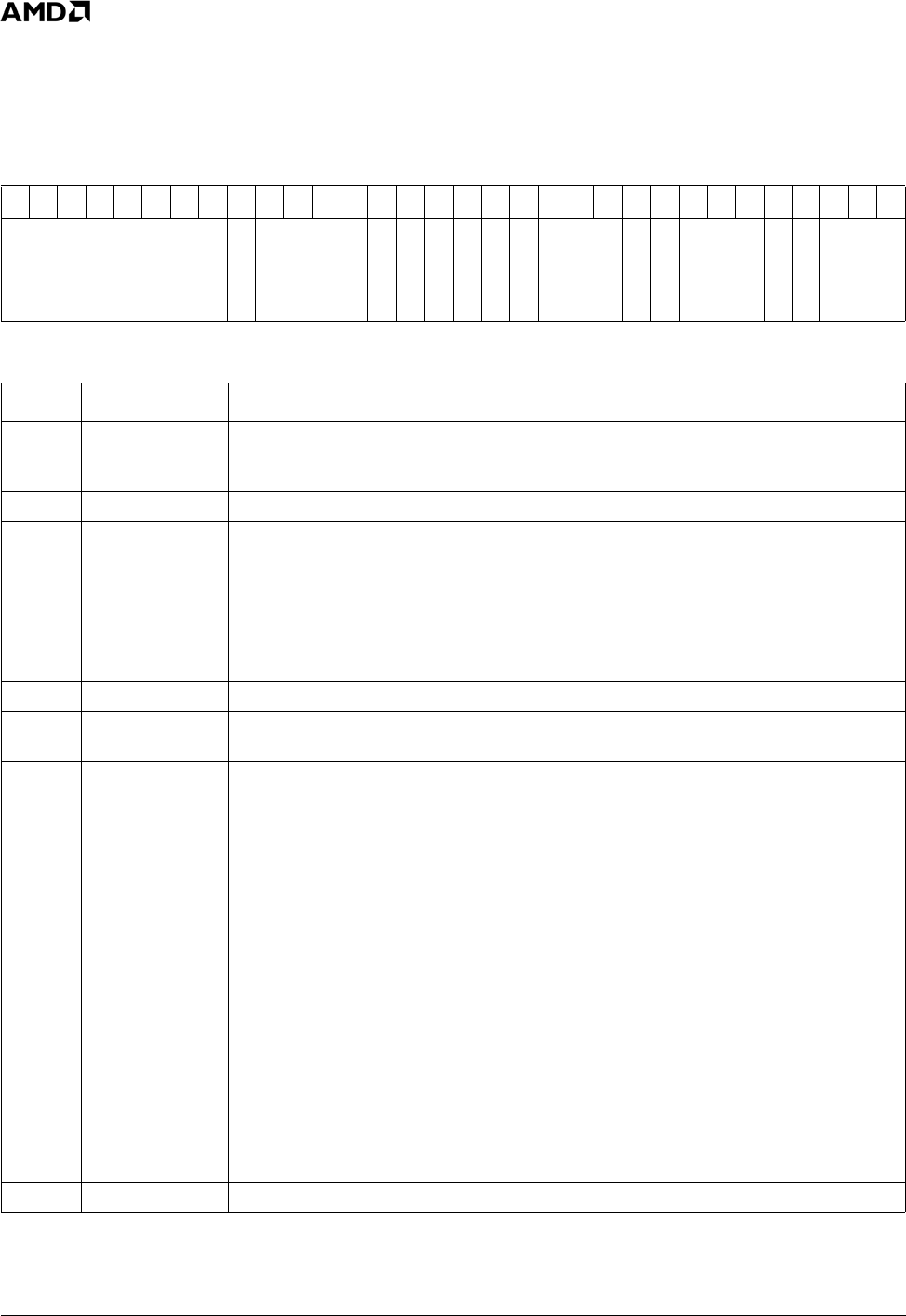

VIP_STATUS Register Map

313029282726252423222120191817161514131211109876543210

APC

RSVD

FPE

RSVD

DPC

SO

BRNU

RSVD

MSG_BERR

B2_FULL

B1_FULL

RSVD

GLWC

FE

RSVD F V

RUN_STATUS

VIP_STATUS Bit Descriptions

Bit Name Description

31:24 APC (RO) Ancillary Packet Count (Read Only). Number of ancillary packets available in the ancil-

lary buffer in system memory. This count is incremented each time an ancillary packet is

received. It gets decremented when a 1 is written to the DPC bit (bit 18).

23 RSVD Reserved.

22:20 FPE (RO) FIFO Pointer Error (Read Only). These bits indicate if the FIFO pointers are misaligned

at the point when the base registers are updated. A 1 indicates that the pointers may be

misaligned, which could result in an horizontal image shift. These bits are valid only when

VBI data reception is disabled. INT15 is generated when any of these bits go active.

[22] - B FIFO.

[21] - R FIFO.

[20] - Y FIFO.

19 RSVD Reserved.

18 DPC (WO) Decrement Ancillary Packet Count (Write Only). Writing a 1 to this bit causes the

ancillary packet count to be decremented by 1.

17 SO (WO) Sync Out (Write Only). Writing a 1 to this bit causes a 0-1-0 transition on the

VIP_VSYNC pin (32 GLIU clocks).

16 BRNU (RO) Base Register Not Updated (Read Only).

0: All base registers are updated.

1: One or more of the base registers have been written but have not yet been updated.

Note: The following base registers are updated at a start-of-frame event.

TASK_A_VID_EVEN_BASE, TASK_A_VID_ODD_BASE, TASK_A_VBI_EVEN_BASE,

TASK_A_VID_ODD_BASE, TASK_A_VID_EVEN_BASE, TASK_A_VID_ODD_BASE,

TASK_A_VBI_EVEN_BASE, TASK_A_VID_ODD_BASE

The start-of-frame event occurs when entering a vertical blanking interval during the Odd

field (for interlaced video) or when entering any vertical blanking interval (non-interlaced

video). Since the base pointers are initialized to 0 at reset, a start-of-frame event MUST

occur before enabling VIP to receive data. Otherwise, VIP will save the first video frame

to address 0 in system memory. One way of insuring this is to initialize VIP to receive

video data with the RUN_MODE bits (VIP Memory Offset 00h bits [7:5]) set to 0. This

enables the VIP input interface, but it will not capture video. Poll this bit until the internal

base register updates have occurred. The RUN_MODE control can then be programmed

to start capturing data on the next line/field/frame boundary.

15 RSVD Reserved.