AMD Geode™ LX Processors Data Book 329

Display Controller Register Descriptions

33234H

6.6.5.2 DC CRT Horizontal Blanking Timing (DC_H_BLANK_TIMING)

This register contains CRT horizontal blank timing information.

Note: A minimum of 32 pixel clocks is required for the horizontal blanking portion of a line in order for the timing generator

to function correctly.

6.6.5.3 DC CRT Horizontal Sync Timing (DC_H_SYNC_TIMING)

This register contains CRT horizontal sync timing information. Note however, that this register should also be programmed

appropriately for flat panel only display, since the horizontal sync transition determines when to advance the vertical

counter.

DC Memory Offset 044h

Typ e R /W

Reset Value xxxxxxxxh

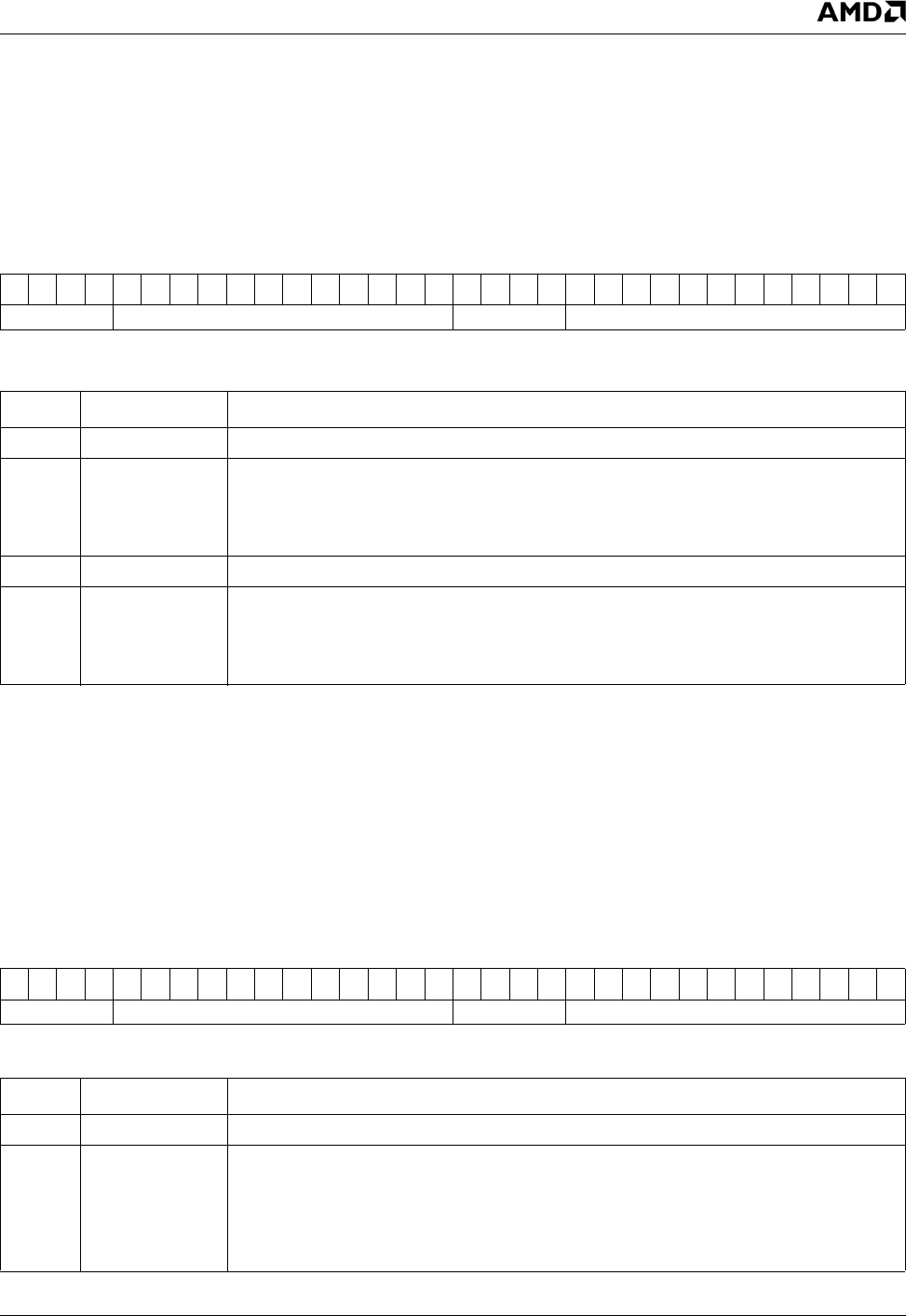

DC_H_BLANK_TIMING Register Map

313029282726252423222120191817161514131211109876543210

RSVD H_BLK_END RSVD H_BLK_START

DC_H_BLANK_TIMING Bit Descriptions

Bit Name Description

31:28 RSVD Reserved. These bits should be programmed to zero.

27:16 H_BLK_END Horizontal Blank End. This field represents the pixel clock count at which the horizontal

blanking signal becomes inactive minus 1.

Unlike previous versions of the DC, this field can be programmed to any pixel granularity;

it is not limited to character (8-pixel) granularity.

15:12 RSVD Reserved. These bits should be programmed to zero.

11:0 H_BLK_START Horizontal Blank Start. This field represents the pixel clock count at which the horizon-

tal blanking signal becomes active minus 1.

Unlike previous versions of the DC, this field can be programmed to any pixel granularity;

it is not limited to character (8-pixel) granularity.

DC Memory Offset 048h

Typ e R /W

Reset Value xxxxxxxxh

DC_H_SYNC_TIMING Register Map

313029282726252423222120191817161514131211109876543210

RSVD H_SYNC_END RSVD H_SYNC_ST

DC_H_SYNC_TIMING Bit Descriptions

Bit Name Description

31:28 RSVD Reserved. These bits should be programmed to zero.

27:16 H_SYNC_END Horizontal Sync End. This field represents the pixel clock count at which the CRT hori-

zontal sync signal becomes inactive minus 1.

Unlike previous versions of the DC, this field can be programmed to any pixel granularity;

it is not limited to character (8-pixel) granularity.

The horizontal sync must be at least 8 pixels in width.