152 AMD Geode™ LX Processors Data Book

CPU Core Register Descriptions

33234H

5.5.2.52 Instruction Cache Index MSR (IC_INDEX_MSR)

5.5.2.53 Instruction Cache Data MSR (IC_DATA_MSR)

MSR Address 00001710h

Typ e R /W

Reset Value 00000000_00000000h

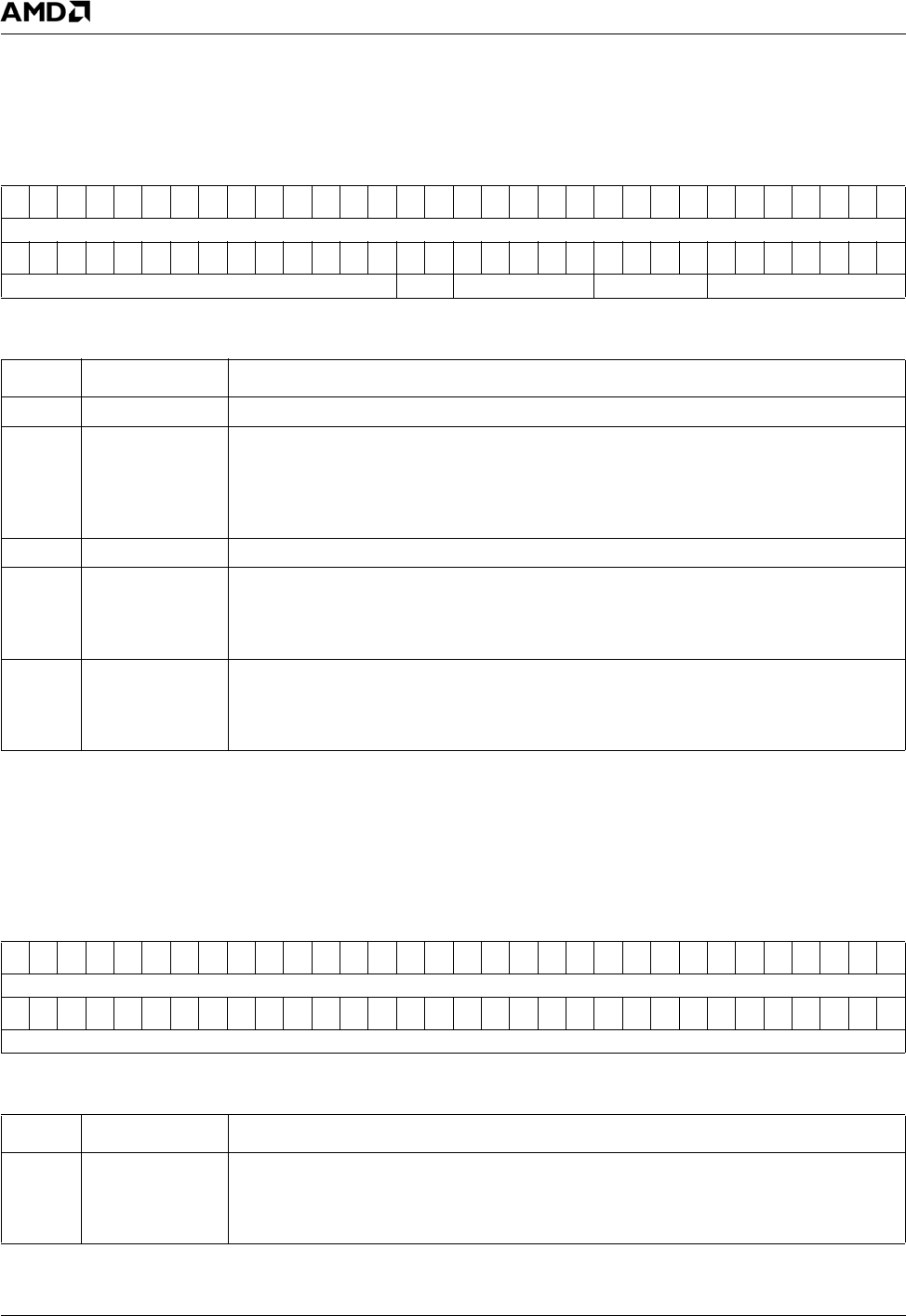

IC_INDEX_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

RSVD DSEL RSVD WAY LINE

IC_INDEX_MSR Bit Descriptions

Bits Name Description

63:18 RSVD (RO) Reserved (Read Only).

17:16 DSEL Data QWORD Select for L1 Cache MSR Access. Determines which QWORD in a

cache line is accessed by a read or a write to IC_DATA_MSR (MSR 00001711h). This

field resets to 0 on any access to IC_TAG_MSR (MSR 00001712h) or IC_TAG_I_MSR

(MSR 00001713h) and increments on access to IC_DATA_MSR. This field is not used

when accessing the L0 cache. (Default = 0)

15:11 RSVD (RO) Reserved (Read Only).

10:7 WAY L1 Cache Way to Access. Forms the high-order bits of an 11-bit counter. The LINE field

(bits [6:0]) forms the low seven bits of the counter. This field increments when the LINE

field overflows on a access to IC_TAG_I_MSR (MSR 00001713h). This field is not used

for the L0 cache. (Default = 0)

6:0 LINE L1 Cache Line to Access. Forms the low-order bits of an 11-bit counter. The WAY field

(bits [3:0]) forms the high four bits of the counter. This field post-increments on an access

to IC_TAG_I_MSR (MSR 00001713h). When accessing the L0 cache, only bits [4:0] are

important and are used to select the line to read in the L0 cache. (Default = 0)

MSR Address 00001711h

Typ e R /W

Reset Value xxxxxxxx_xxxxxxxxh

IC_DATA_MSR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

DATA (Upper)

313029282726252423222120191817161514131211109876543210

DATA (Lower)

IC_DATA_MSR Bit Descriptions

Bits Name Description

63:0 DATA QWORD to Read from or Write to the L1 Cache. The address to the QWORD specified

by the LINE and DSEL fields from IC_INDEX_MSR (MSR 00001710h). The way in the

cache to read and write is specified by the WAY field in IC_INDEX_MSR. Each access to

IC_DATA_MSR increments DSEL.