378 AMD Geode™ LX Processors Data Book

Display Controller Register Descriptions

33234H

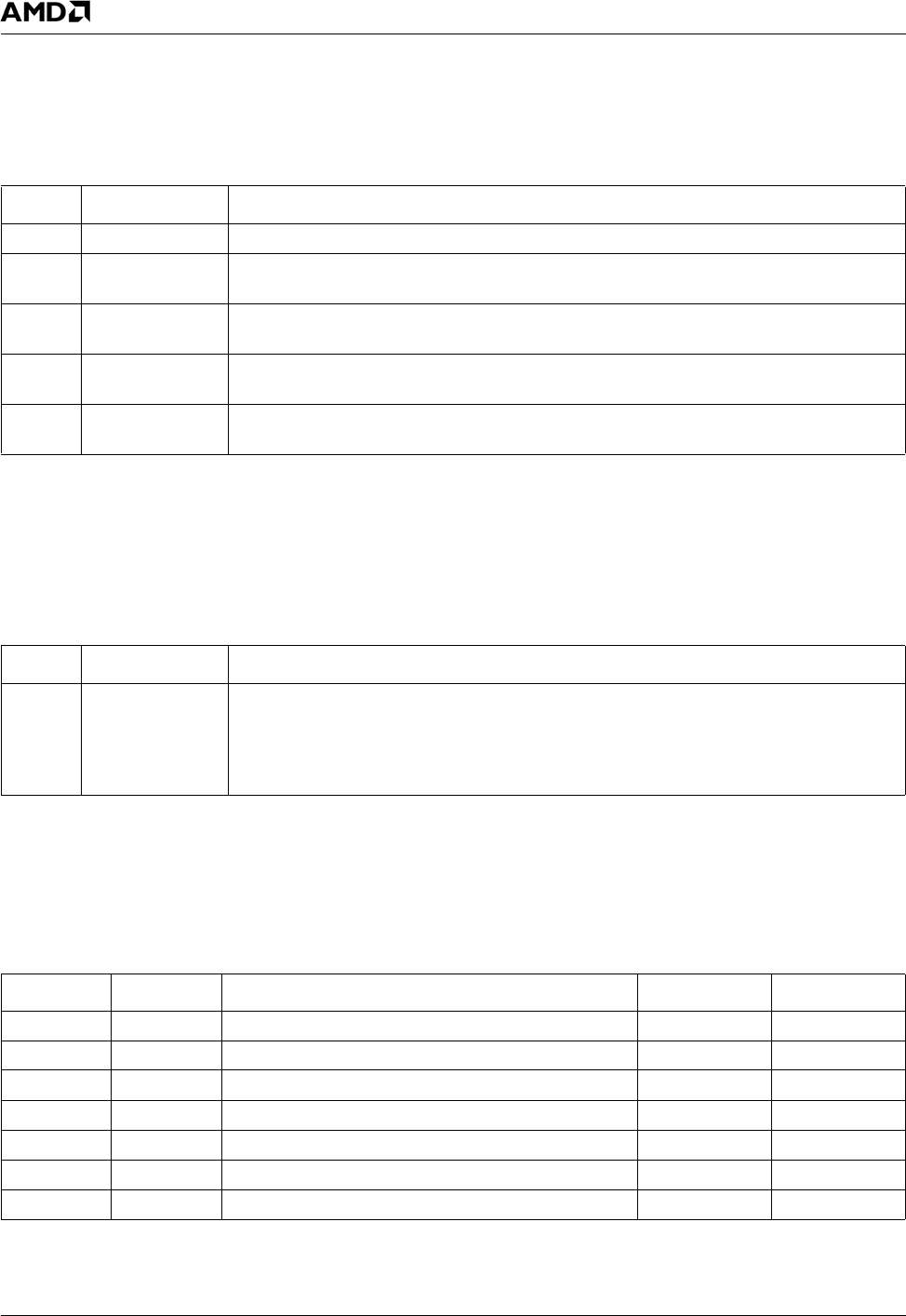

6.6.20.10 VGA Color Don’t Care

6.6.20.11 VGA Bit Mask

6.6.21 Attribute Controller Registers

The attribute controller registers are accessed by writing an index value to the Attribute Controller Index register (3C0h) and

reading or writing the register using the Attribute Controller Data register (3C0h for writes, 3C1h for reads).

Index 07h

Typ e R /W

Reset Value xxh

VGA Color Don’t Care Register Bit Descriptions

Bit Name Description

7:4 RSVD Reserved.

3CM_PR3 Compare Map 3. This bit enables (bit = 1) or excludes (bit = 0) map 3 from participating

in a color compare operation.

2CM_PR2 Compare Map 2. This bit enables (bit = 1) or excludes (bit = 0) map 2 from participating

in a color compare operation.

1CM_PR1 Compare Map 1. This bit enables (bit = 1) or excludes (bit = 0) map 1 from participating

in a color compare operation.

0CM_PR0 Compare Map 0. This bit enables (bit = 1) or excludes (bit = 0) map 0 from participating

in a color compare operation.

Index 08h

Typ e R /W

Reset Value xxh

VGA Bit Mask Register Bit Descriptions

Bit Name Description

7:0 BT_MSK Bit Mask. The bit mask is used to enable or disable writing to individual bits in each map.

A 1 in the bit mask allows a bit to be updated, while a 0 in the bit mask writes the contents

of the data latches back to memory, effectively protecting that bit from update. The data

latches must be set by doing a frame buffer read in order for the masking operation to

work properly. The bit mask is used in write modes 0, 2, and 3.

Table 6-57. Attribute Controller Registers Summary

Index Type Register Reset Value Reference

-- R/W Attribute Controller Index/Data/Data xxh Page 379

00h-0Fh R/W EGA Palette xxh Page 379

10h R/W Attribute Mode Control xxh Page 380

11h R/W Overscan Color xxh Page 380

12h R/W Color Plane Enable xxh Page 381

13h R/W Horizontal Pel Panning xxh Page 381

14h R/W Color Select xxh Page 382