AMD Geode™ LX Processors Data Book 443

Video Processor Register Descriptions

33234H

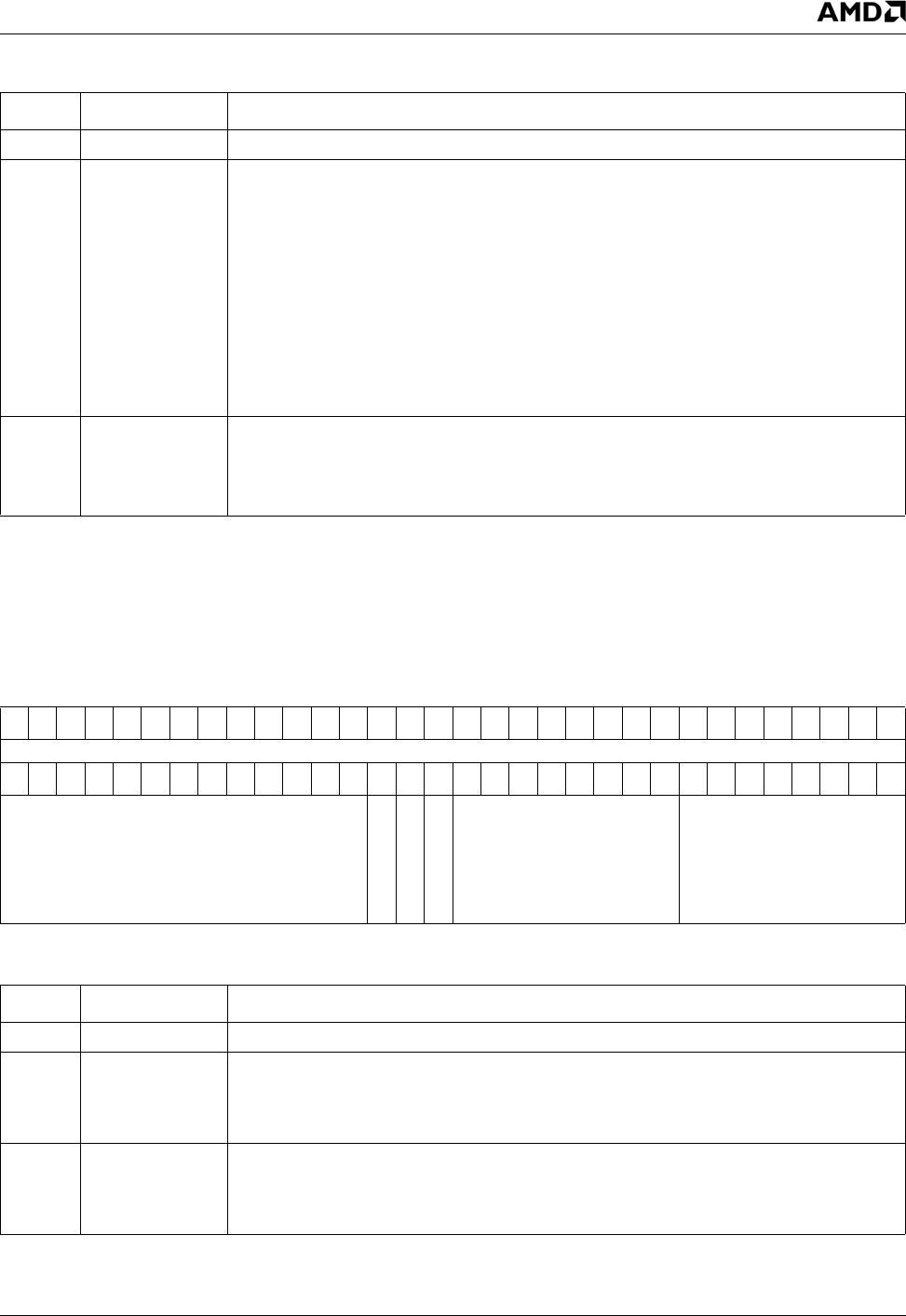

6.8.3.30 Alpha Window 2 Control (A2T)

A2C Bit Descriptions

Bit Name Description

63:25 RSVD (RO) Reserved (Read Only). Reads back as 0.

24 ALPHA2_

COLOR_REG_

EN

Alpha Window 2 Color Register Enable. Enable bit for the color key matching in alpha

window 2.

0: Disable. If this bit is disabled, the alpha window is enabled, and VG_CK = 0 (VP Mem-

ory Offset 008h[20]); then where there is a color key match within the alpha window,

video is displayed.

If this bit is disabled, the alpha window is enabled, and VG_CK = 1 (VP Memory Offset

008h[20]); then where there is a chroma-key match within the alpha window, graphics

are displayed. See Figure 6-31 on page 438.

1: Enable. If this bit is enabled and the alpha window is enabled, then where there is a

color key match within the alpha window; the color value in ALPHA2_COLOR_REG

(bits [23:0]) is displayed.

23:0 ALPHA2_

COLOR_REG

Alpha Window 2 Color Register. Specifies the color to be displayed inside the alpha

window when there is a color key match in the alpha window.

This color is only displayed if the alpha window is enabled and

ALPHA2_COLOR_REG_EN (bit 24) is enabled.

VP Memory Offset 0F8h

Typ e R /W

Reset Value 00000000_00000000h

A2T Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

313029282726252423222120191817161514131211109876543210

RSVD

PPA2_EN

LOAD_ALPHA

ALPHA2_WIN_EN

ALPHA2_INC ALPHA2_MUL

A2T Bit Descriptions

Bit Name Description

63:19 RSVD (RO) Reserved (Read Only). Reads back as 0.

18 PPA2_EN Per-Pixel Alpha Window 2 Enable. Enable per-pixel alpha functionality for alpha win-

dow 2.

0: Single alpha value for entire alpha window 2 (ALPHA2_MUL).

1: Each pixel has its own alpha value defined in the upper 8 bits of the graphics bus.

17 LOAD_ALPHA Load Alpha (Write Only). When set to 1, this bit causes the Video Processor module to

load the alpha value (bits [31:24] of the video data path) multiplied with the alpha multi-

plier (ALPHA2_MUL, bits [7:0]) at the start of the next frame. This bit is cleared by the de-

assertion of VSYNC.