596 AMD Geode™ LX Processors Data Book

GeodeLink™ PCI Bridge Register Descriptions

33234H

6.16.2.17 GLPCI General Purpose I/O (GLPCI_GPIO)

MSR Address 50002020h

Typ e R /W

Reset Value 00000000_00000000h

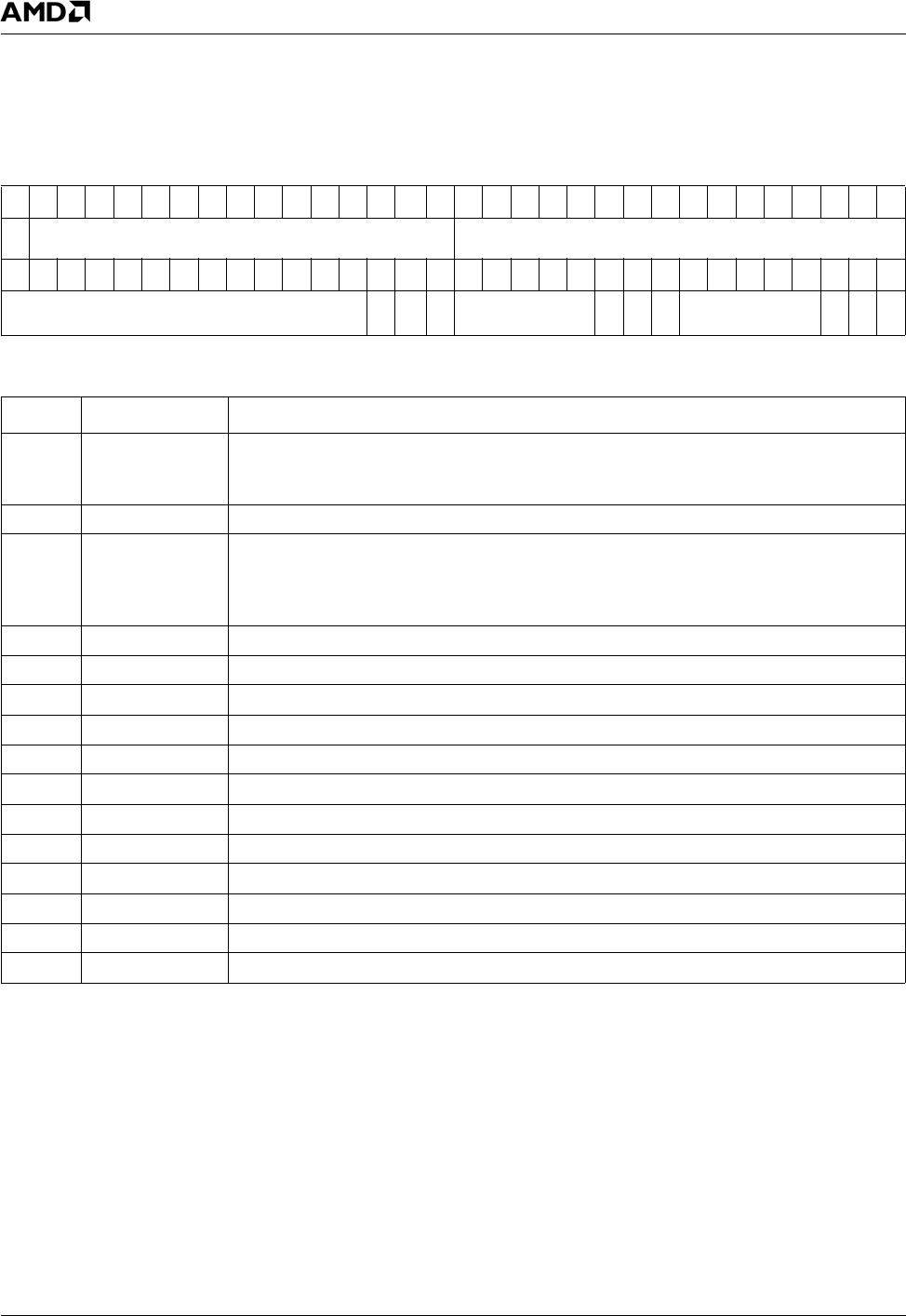

GLPCI_GPIO Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

MSW

RSVD SAMPDIV

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RSVD

OE2

OE1

OE0

RSVD

OUT2

OUT1

OUT0

RSVD

IN2

IN1

IN0

GLPCI_GPIO Register Bit Descriptions

Bit Name Description

63 MSW Most Significant Word Enable. Must be set on writes to alter SAMPDIV (bits [47:32]).

When cleared, the SAMPDIV field will not be updated. When set, the SAMPDIV field will

be written.

62:48 RSVD (RO) Reserved (Read Only). Reserved for future use.

47:32 SAMPDIV Sample Divider. Controls the frequency of sampling input data fed into each filter. With a

value of zero, each input is sampled on every PCI clock edge. With a value of 1, each

input is sampled every other clock edge. With a value of 2, it is sampled every third clock

edge, and so on.

31:19 RSVD (RO) Reserved (Read Only). Reserved for future use.

18 OE2 Output Enable 2. Output enable for GNT2# pin.

17 OE1 Output Enable 1. Output enable for REQ1# pin.

16 OE0 Output Enable 0. Output enable for GNT1# pin.

15:11 RSVD (RO) Reserved (Read Only). Reserved for future use.

10 OUT2 Output 2. Output for GNT2# pin.

9OUT1 Output 1. Output for REQ1# pin.

8OUT0 Output 0. Output for GNT1# pin.

7:3 RSVD (RO) Reserved (Read Only). Reserved for future use.

2IN2 (RO) Input 2 (Read Only). Filtered input from GNT2# pin.

1IN1 (RO) Input 1 (Read Only). Filtered input from REQ1# pin.

0IN0 (RO) Input 0 (Read Only). Filtered input from GNT1# pin.