AMD Geode™ LX Processors Data Book 309

Display Controller Register Descriptions

33234H

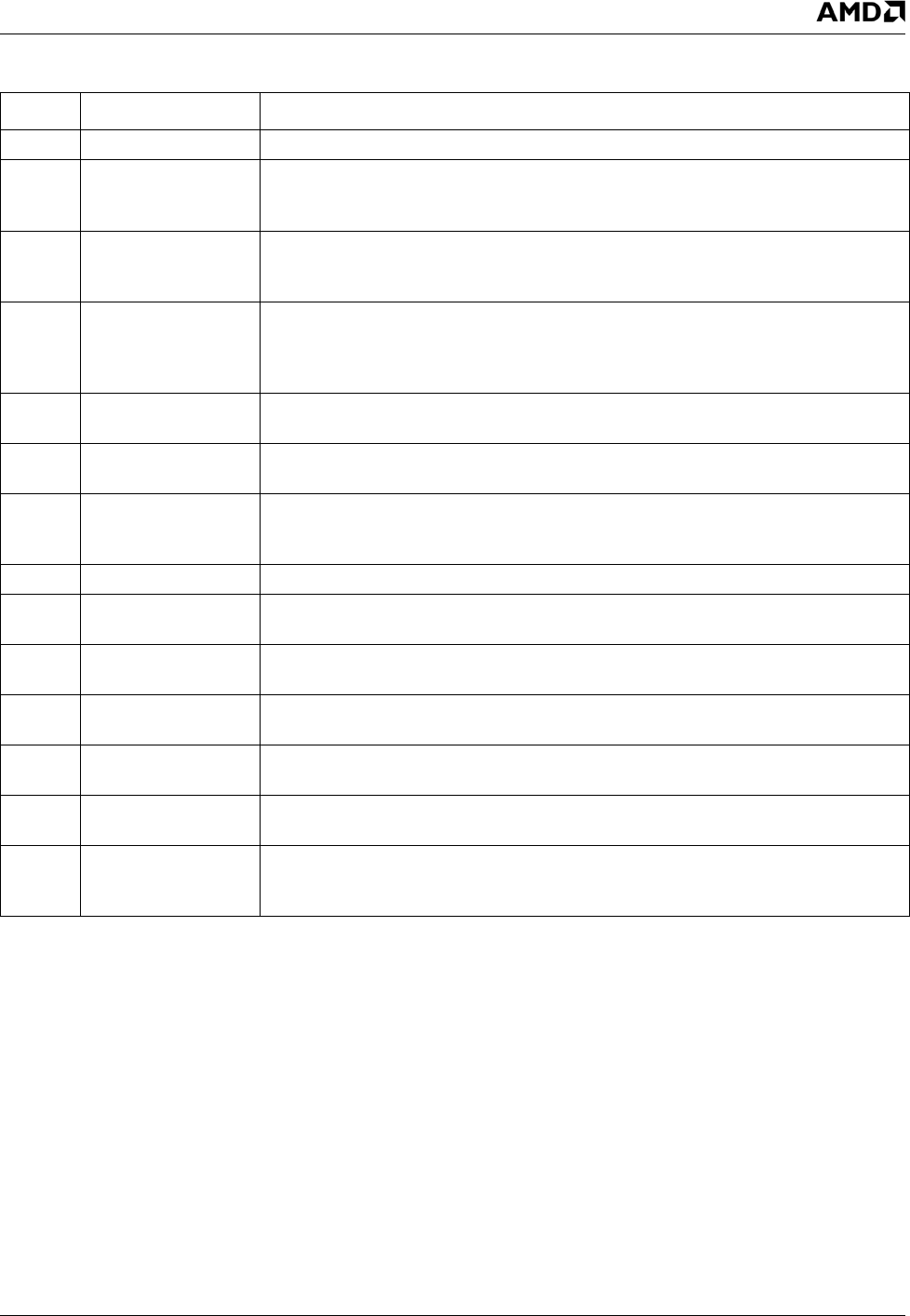

GLD_MSR_ERROR Bit Descriptions

Bit Name Description

63:38 RSVD Reserved. Set to 0.

37 CWD_CHECK_ERR Control Word Check Error. Reading a 1 indicates that an invalid control word was

read from the Display FIFO, which is indicative of a FIFO underrun. Writing a 1 to this

bit clears it.

36 SYNCBUF_ERR Synchronizer Buffer Error. Reading a 1 indicates that the display pipe attempted to

read the synchronizer buffer while it was invalid. This is indicative of a synchronizer

buffer underrun. Writing a 1 to this bit clears it.

35 DFIFO_ERR Display FIFO Underrun Error. Reading a 1 indicates that the asynchronous error

signal is being driven because the display FIFO has “run dry”. This implies that at

least one frame of the display was corrupted. Writing a 1 to this bit clears it; writing a

0 has no effect.

34 SMI_ERR Uncleared SMI Error. Reading a 1 indicates that the asynchronous error signal is

being driven because a second SMI occurred while the first SMI went unserviced.

33 ADDR_ERR Unexpected Address Error. Reading a 1 indicates that the exception flag was set

because the DC received a GLIU0 transaction request.

32 TYPE_ERR Unexpected Type Error. Reading a 1 indicates that an asynchronous error has

occurred because the DC received a GLIU0 transaction with an undefined or unex-

pected type.

31:6 RSVD Reserved. Set to 0.

5 CWD_CHECK_MSK Control Word Check Error Mask. When set to 1, disables generation of the asyn-

chronous error signal when an invalid control word is read from the data FIFO.

4 SYNCBUF_MSK Synchronizer Buffer Error Mask. When set to 1, disables generation of the asyn-

chronous error signal when invalid data is read from the synchronizer buffer.

3 DFIFO_ERR_MASK Display FIFO Underrun Error Mask. When set to 1, disables generation of the asyn-

chronous error signal when at least one frame of the display was corrupted.

2 SMI_ERR_MASK Uncleared SMI Error Mask. When set to 1, disables generation of the asynchronous

error signal when a second SMI occurred while the first SMI went unserviced.

1 ADDR_ERR_MASK Unexpected Address Error Mask. When set to 1, disables generation of an excep-

tion flag when the DC receives a GLIU0 request.

0 TYPE_ERR_MASK Unexpected Type Error Mask. When set to 1, disables generation of the asynchro-

nous error signal when the DC received a GLIU0 transaction with an undefined or

unexpected type.