AMD Geode™ LX Processors Data Book 533

GeodeLink™ Control Processor

33234H

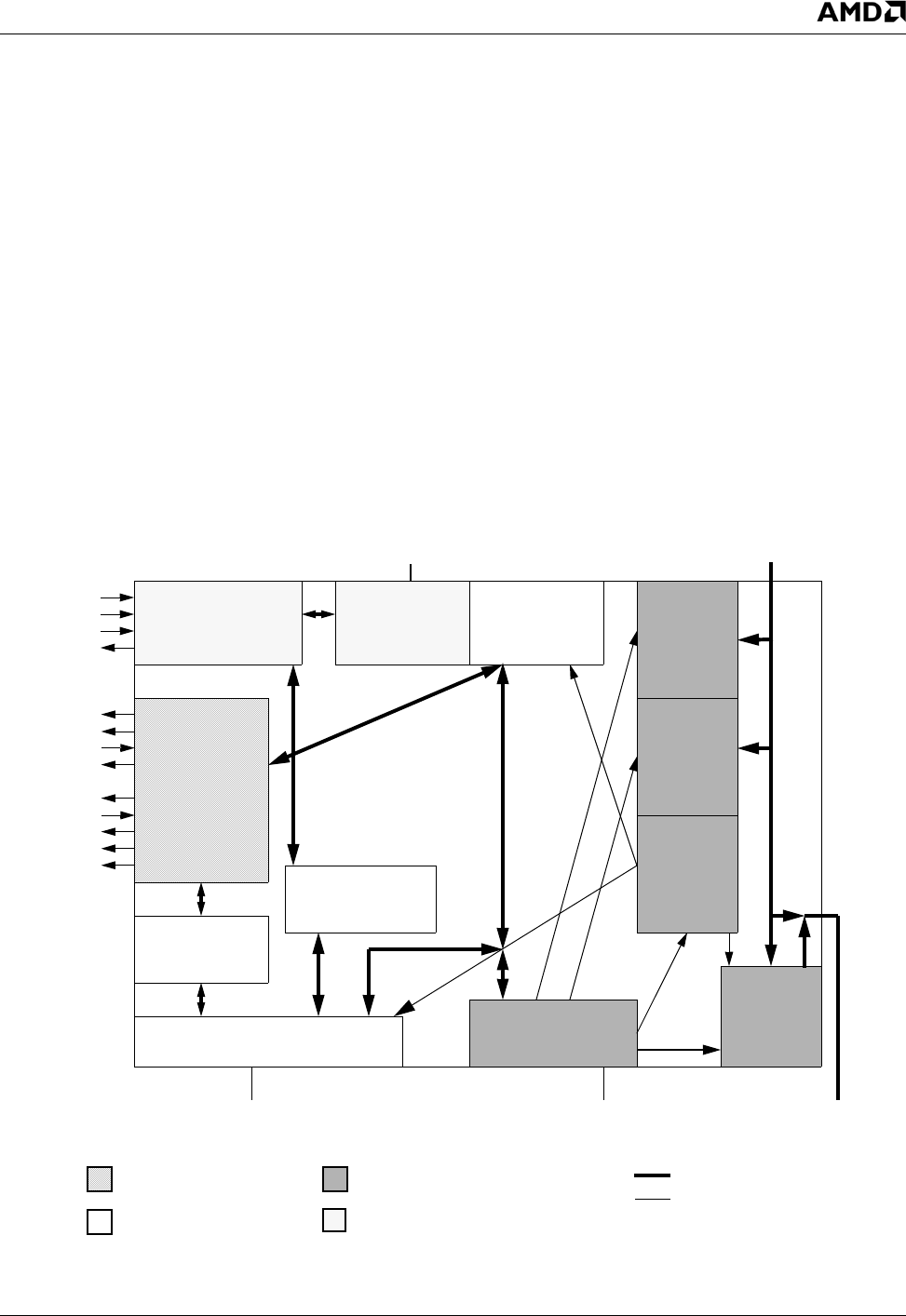

6.13 GeodeLink™ Control Processor

The GeodeLink Control Processor (GLCP) functionality

covers these areas (see Figure 6-55):

• Scan chain control

• JTAG interface to boundary scan, BIST, GLIU1, and

debug logic

• Power (clock) control

• Reset logic

• PLL control

• Internal logic analyzer/debugger

• 1KB FIFO/SRAM

• Compliant with GLIU System Architecture Specification

v1.07

• Supports AMD Geode™ CS5536 companion device

interface

• Supports physical pins for SUSPA# and IRQ13

• Supports muxed pin for SUSP#

6.13.1 TAP Controller

The TAP controller is IEEE 1149.1 compliant. TMS, TDI,

TCLK, and TDO are directly supported (TRST is available

as a bootstrap pin during reset, but is always inactive if the

system reset is inactive). The Instruction register (IR) is 25

bits wide. The meanings of the various instructions are

shown in Table 6-81 on page 534 along with the length of

the Data register that can be accessed once the instruction

is entered. All Data registers shift in and out data, LSB first.

The Instruction and all Data registers are shift registers, so

if more bits are shifted in than the register can hold, only

the last bits shifted in (the MSBs) are used.

The TAP controller has specific pre-assigned meanings to

the bits in the 25-bit IR. The meanings are summarized in

Table 6-82 on page 534. Note that the bits only affect the

chip once the “Update-IR” JTAG state occurs in the JTAG

controller. Shifting through these bits does not change the

state of internal signals (for example TEST_MODE). For

details on JTAG controller states, refer to the IEEE Stan-

dard 1149.1-1990.

Figure 6-55. GLCP Block Diagram

Debug

Debug

Action

Decode

GLIU Interface

Debug

Control

Diagnostic Bus

Scan, BIST, Clock, Reset, Suspend Signals

TCLK

TMS

TDI

TDO

rqin, rqout, dain, daout

Off-Chip

Diagnostic Pins

GLIU Clock Frequency

Debug Clock Frequency (varies)

TCLK Clock Frequency

Data and Control Buses

Control Only

Event

Generator

IEEE 1149.1

Interface

Comparators

Clock, Reset,

ACPI Control

Scan and BIST

Control

Serial-to-GLIU

Conversion

128 WORD

64-Bit

FIFO

TDBGI, TDBGO

IRQ13

INTA#

SUSP#

SUSPA#

GIO_IGNNE

VA_FERR

GIO_NMI

GIO_INIT

GIO_INTR

PCI Clock Frequency

GIO

Synchronizing

AMD Geode™

Companion

Device

Interface

(GIO)