512 AMD Geode™ LX Processors Data Book

Security Block

33234H

6.11.2.1 EEPROM ID Interface

The EEPROM ID interface provides an interface to an

EEPROM non-volatile memory available for storing ID

numbers, keys, or other security related information. The

EEPROM ID interface consists of a 2K (256-byte) array

with 2 bytes reserved for EEPROM control state, 238 bytes

are available as general purpose non-volatile storage, and

16 bytes reserved for use as a hidden key for the AES

engine. (Note that locations 18-33 are reserved for a

Unique ID, but can be used for general purpose storage.)

After reset, the EEPROM ID interface state machine reads

the two access control bytes from the EEPROM. These

define the access policies for the EEPROM. It also auto-

matically copies the 128-bit hidden key from the array to

the AES engine’s hidden key register. When an

AMD Geode LX processor device is initially manufactured,

the EEPROM is programmed to all ones and the control

bytes are set to the unlocked state allowing writing of the

entire EEPROM array and reading of all location except the

hidden key. Information can be stored in the EEPROM and

then optionally the EEPROM can be locked to prevent fur-

ther writes and/or disable certain debug features of the

AMD Geode LX processor.

The EEPROM controller defaults to the unlocked state if it

cannot access an EEPROM after reset. This allows parts

built without EEPROMs to have functional debug inter-

faces.

The EEPROM ID interface works on a byte-wide basis. The

EEPROM Address register (SB Memory Offset 804h) is

first programmed by software, and then the EEPROM

Command register (SB Memory Offset 804h) is written to

initiate a write from the EEPROM Data register (SB Mem-

ory Offset 808h) to the array or a read from the array to the

Data register. The START bit in the Command register (SB

Memory Offset 800h) resets automatically once the

EEPROM access has completed. The user may also

enable an interrupt to be generated when the access has

completed. Since the EEPROM access is slow, this simple

command interface allows the processor to continue with

other tasks while waiting for the access to complete. Table

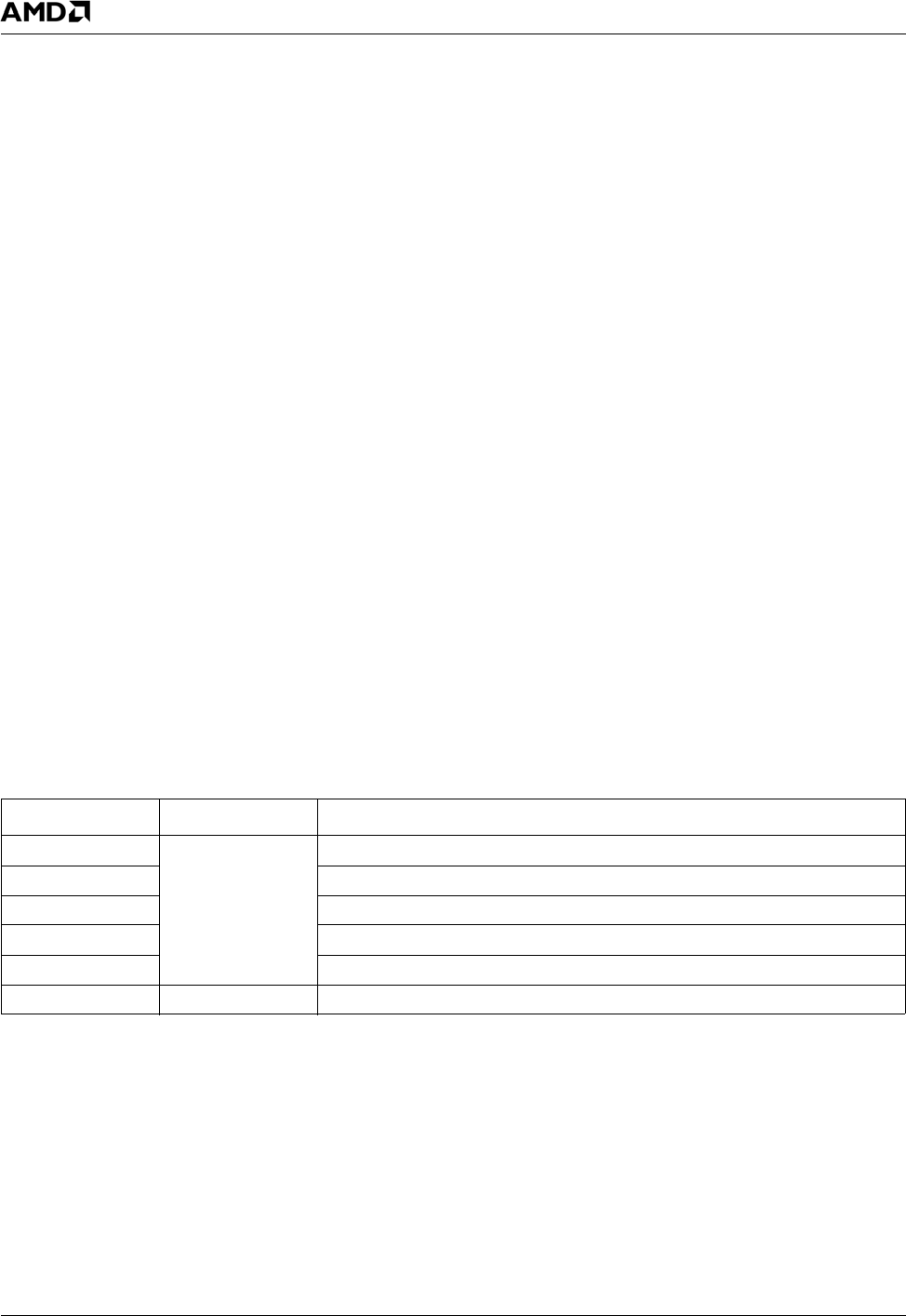

6-77 shows common usage of the EEPROM.

Note: The EEPROM interface is designed to work with a

GLIU frequency up to 400 MHz. For operation

above 400 MHz, several internal design parame-

ters must be changed.

6.11.2.2 Security Block Interrupts

The Security Block has three possible sources for an inter-

rupt: completion of an AES task on context A, completion

of an AES task on context B, and completion of an

EEPROM read or write operation. The interrupt event and

interrupt mask registers are memory mapped. These three

sources can also generate an SMI. The SMI event and SMI

mask registers are accessible via MSRs. Any one of these

events will simultaneously set the SMI and interrupt event

bits. The mask bits may be used to enable either an inter-

rupt or an SMI if desired.

6.11.2.3 GLIU Interface

The GLIU provides a standard interface to the AMD Geode

LX processor. The Security Block is both a master and a

slave on this bus.

Table 6-77. EEPROM Address Map

Byte Address Range Description

0 Lower Access control byte 0 (WPU and WPL)

1 Access control byte 1 (WPE and DBL)

2-17 Hidden key storage (128 bits)

18-33 Unique ID (128 bits)

34-127 User data

128-255 Upper User data