AMD Geode™ LX Processors Data Book 21

3

Signal Definitions 33234H

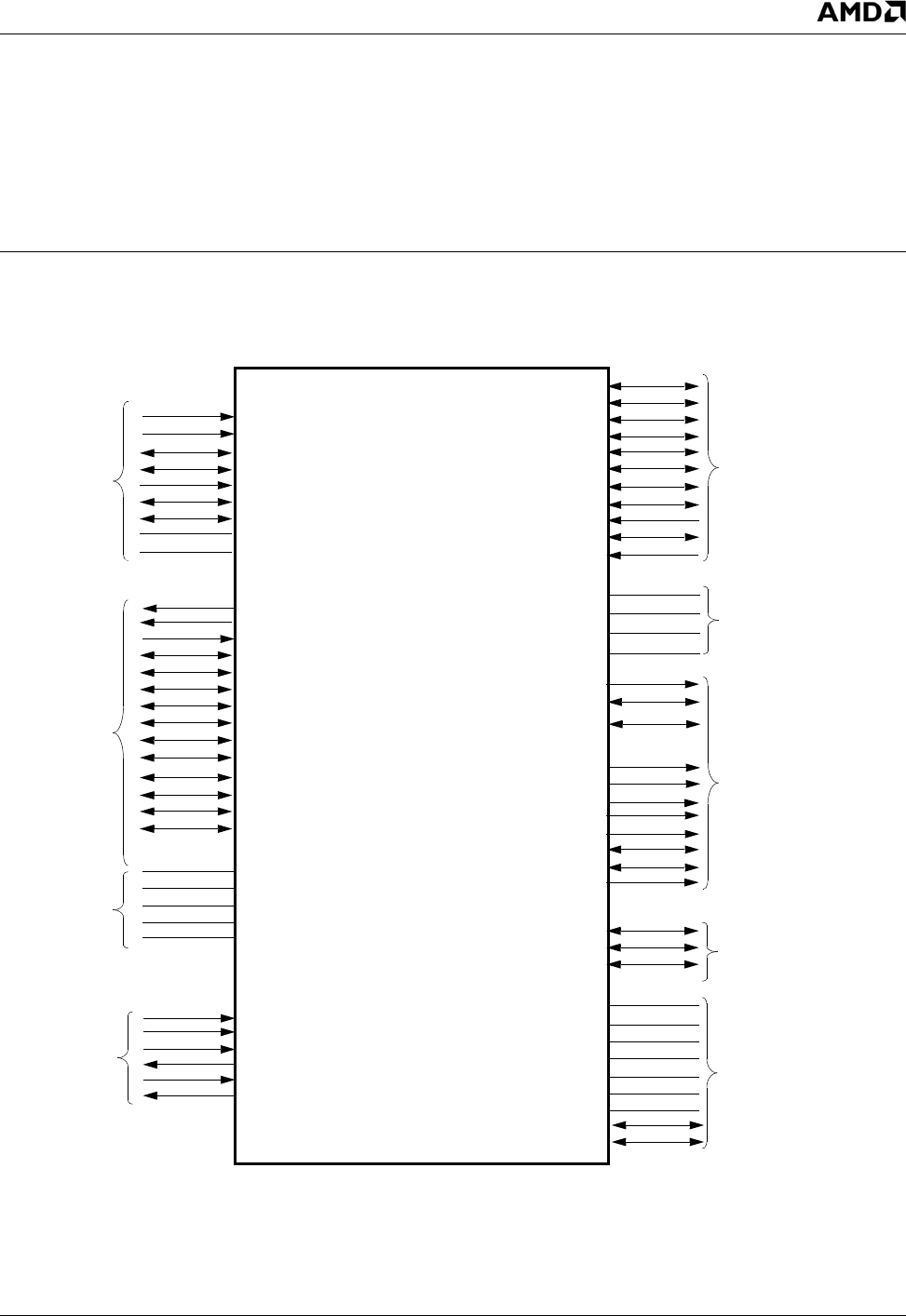

3.0Signal Definitions

This chapter defines the signals and describes the external interface of the AMD Geode™ LX processor. Figure 3-1 shows

the pins organized by their functional groupings. Where signals are multiplexed, the default signal name is listed first and is

separated by a plus sign (+). Multi-function pins are described in Table 3-1 on page 22.

Figure 3-1. Signal Groups

RESET#

INTA#

IRQ13 (STRAP)

SDCLK[5:0]N

CKE[1:0]

CS[3:0]#

RAS[1:0]#

CAS[1:0]#

WE[1:0]#

DQM[7:0]

DQS[7:0]

BA[1:0]

DQ[63:0]

MA[13:0]

AD[31:0]

CBE[3:0]#

FRAME#

IRDY#

TRDY#

STOP#

DEVSEL#

DOTREF

PAR

(STRAP)

GNT[2:0]#

CIS

SUSPA# (STRAP)

TDP

TDN

System

Memory

Display (TFT Option)

VDDEN+VIP_HSYNC

DRGB[25:24]+VID[9:8]+

DOTCLK+VOPCLK

VSYNC+VOP_VSYNC

HSYNC+VOP_HSYNC

GREEN

BLUE

RED

LDEMOD+VIP_VSYNC

SYSREF

TLA[1:0]

REQ[2:0]#

VID[7:0]

VIPCLK

VIPSYNC

VIP

PW[1:0] (STRAP)

(Total of 32) V

CORE

(Total of 33) V

MEM

(Total of 128) V

SS

(Total of 30) V

IO

Power/Ground

Interface

TCLK

TMS

TDI

TDO

TDBGI

TDBGO

Internal Test

and

Measurement

AMD Geode™

VAV

DD

, CAV

DD

, MAV

DD

VAV

SS

, CAV

SS

, MAV

SS

MVREF

Display (CRT Option)

DVREF

DRSET

(Total of 4) DAV

DD

(Total of 4) DAV

SS

DISPEN+VOP_BLANK

CLPF

MLPF

VLPF

LX Processor

PLL

PCI

Interface

Signals

Signals

Interface

Signals

Interface

Signals

Interface

Signals

Interface

Signals

Interface

Signals

Interface

Signals

Interface

Signals

SDCLK[5:0]P

VSYNC

HSYNC

DRGB[23:16]

DRBG[15:8]+VOP[15:8]

DRGB[7:0]+VOP[7:0]

MSGSTART+MSGSTOP

DRGB[31:26]+VID[15:10]