AMD Geode™ LX Processors Data Book 623

Instruction Set

33234H

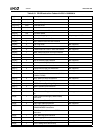

01 000 DS:[BX+SI+d8] DS:[EAX+d8]

01 001 DS:[BX+DI+d8] DS:[ECX+d8]

01 010 SS:[BP+SI+d8] DS:[EDX+d8]

01 011 SS:[BP+DI+d8] DS:[EBX+d8]

01 100 DS:[SI+d8] s-i-b is present (See Table 8-15 on page 626)

01 101 DS:[DI+d8] SS:[EBP+d8]

01 110 SS:[BP+d8] DS:[ESI+d8]

01 111 DS:[BX+d8] DS:[EDI+d8]

10 000 DS:[BX+SI+d16] DS:[EAX+d32]

10 001 DS:[BX+DI+d16] DS:[ECX+d32]

10 010 SS:[BP+SI+d16] DS:[EDX+d32]

10 011 SS:[BP+DI+d16] DS:[EBX+d32]

10 100 DS:[SI+d16] s-i-b is present (See Table 8-15 on page 626)

10 101 DS:[DI+d16] SS:[EBP+d32]

10 110 SS:[BP+d16] DS:[ESI+d32]

10 111 DS:[BX+d16] DS:[EDI+d32]

11 xxx See Table 8-9. See Table 8-9

Note 1. d8 refers to 8-bit displacement, d16 refers to 16-bit displacement, and d32 refers to a 32-bit displacement.

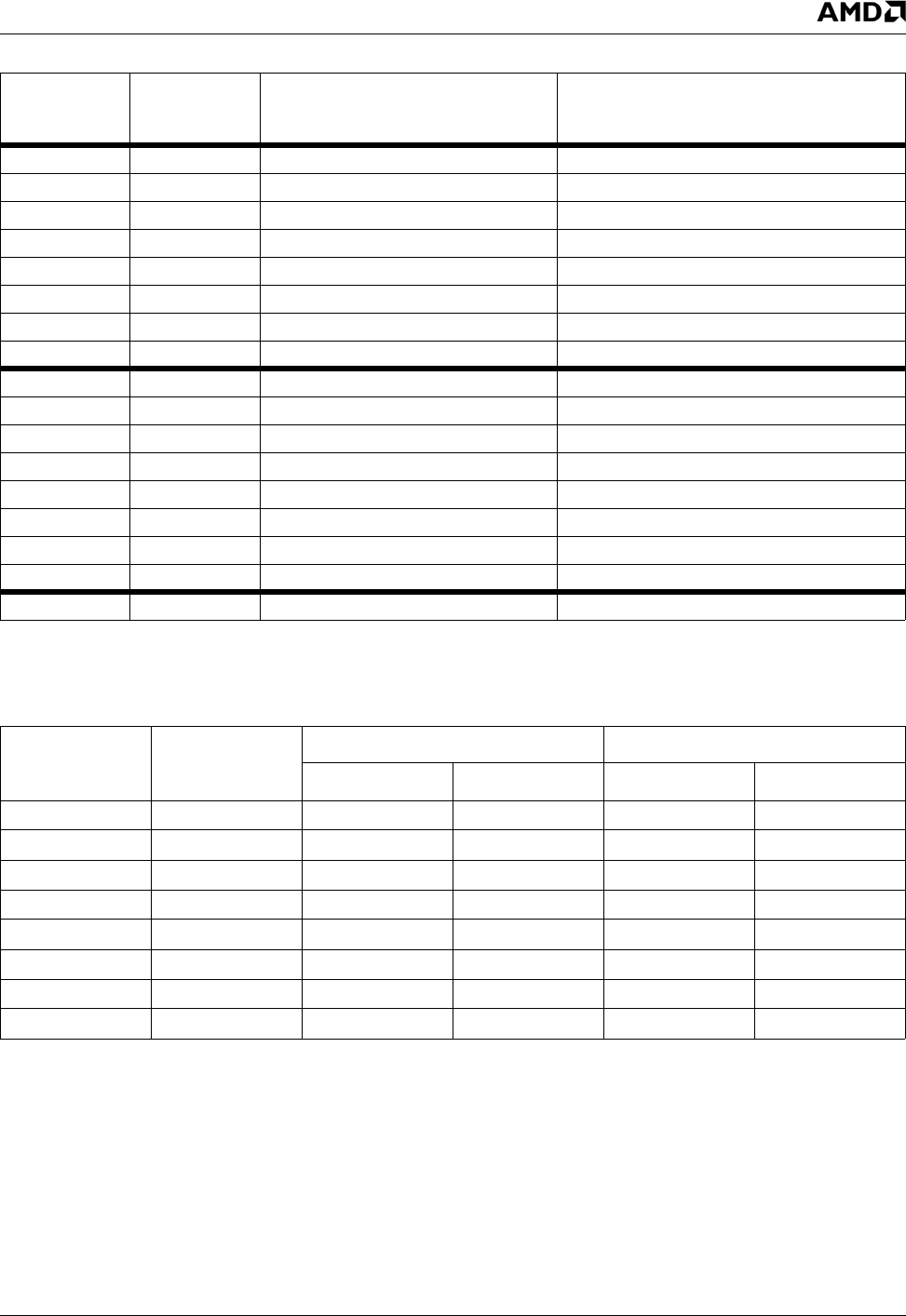

Table 8-9. General Registers Selected by mod r/m Fields and w Field

mod r/m

16-Bit Operation 32-Bit Operation

w = 0 w = 1 w = 0 w = 1

11 000 AL AX AL EAX

11 001 CL CX CL ECX

11 010 DL DX DL EDX

11 011 BL BX BL EBX

11 100 AH SP AH ESP

11 101 CH BP CH EBP

11 110 DH SI DH ESI

11 111 BH DI BH EDI

Table 8-8. mod r/m Field Encoding (Continued)

mod Field r/m Field

16-Bit Address Mode with

mod r/m Byte (Note 1)

32-Bit Address Mode with mod r/m Byte and

No s-i-b Byte Present

(Note 1)