404 AMD Geode™ LX Processors Data Book

Video Processor

33234H

6.7.6.6 New VIP 2.0 Video Flags

Four bits are defined (shown in Table 6-64) by the VIP

specification that allow the VIP slave to communicate field/

frame-specific information to the graphics chip during the

video stream output. These flags are embedded in the

lower nibble of the SAV or EAV header. These video flags

allow the graphics chip to handle Bob and Weave, as well

as 3:2 pull-down in hardware. Only bit 3 is implemented in

the AMD Geode LX processor.

6.7.6.7 BT.601 Support

When VOP is configured for BT.601 mode, the HSYNCs

and VSYNCs are used to determine the timing of each data

line sent out. The SAV/EAV codes are not used.

6.7.6.8 VIP 2.0 Level System

For even field detection, some devices require a shift in

VSYNC with respect to HSYNC. This shift is programmed

at DC Memory Offset 080h. Also for correct odd/even field

shift, VP Memory Offset 800h[6] = 1.

6.7.6.9 VBI Data

Vertical Blanking Interval (VBI) data is not part of the active

video (i.e., not directly displayed). This data is sent

between fields of active video data during vertical blanking.

VBI data has many uses: closed captioning, timecodes,

teletext, etc. Although there are some specified standards

with respect to closed captioning which are generally

decoded at the TV, basically, as long as the data is sent

and received correctly, there are no restrictions.

Indication of VBI data is configurable for the different

modes.

In BT.656 mode, typically the TASK bit in the EAV/SAV

header is fixed at 1. In this case, there is no indication of

VBI data. If the VBI bit in the VOP Configuration register is

set to 1 (VP Memory Offset 800h[11] = 1), then VBI data

will be indicated by a TASK bit value of 0 (active video has

the value of 1).

In VIP 1.1 mode, by definition the TASK bit in the EAV/SAV

header is 0 for VBI data, and 1 for active video. The VBI bit

in the VOP Configuration register has no effect in this

mode.

In VIP 2.0 mode, the TASK bit value in the EAV/SAV

header is configurable by selecting a value for the TASK bit

in the VOP Configuration register. If it is desired to have

the TASK bit in the EAV/SAV header indicate VBI data,

then setting the VBI bit will use the inverse value of the

TASK bit in the VOP Configuration register to indicate VBI

data (i.e., if TASK = 1, then VBI data is indicated by a

TASK bit value of 0 in the EAV/SAV, if TASK = 0, then VBI

data is indicated by a TASK bit value of 1 in the EAV/SAV).

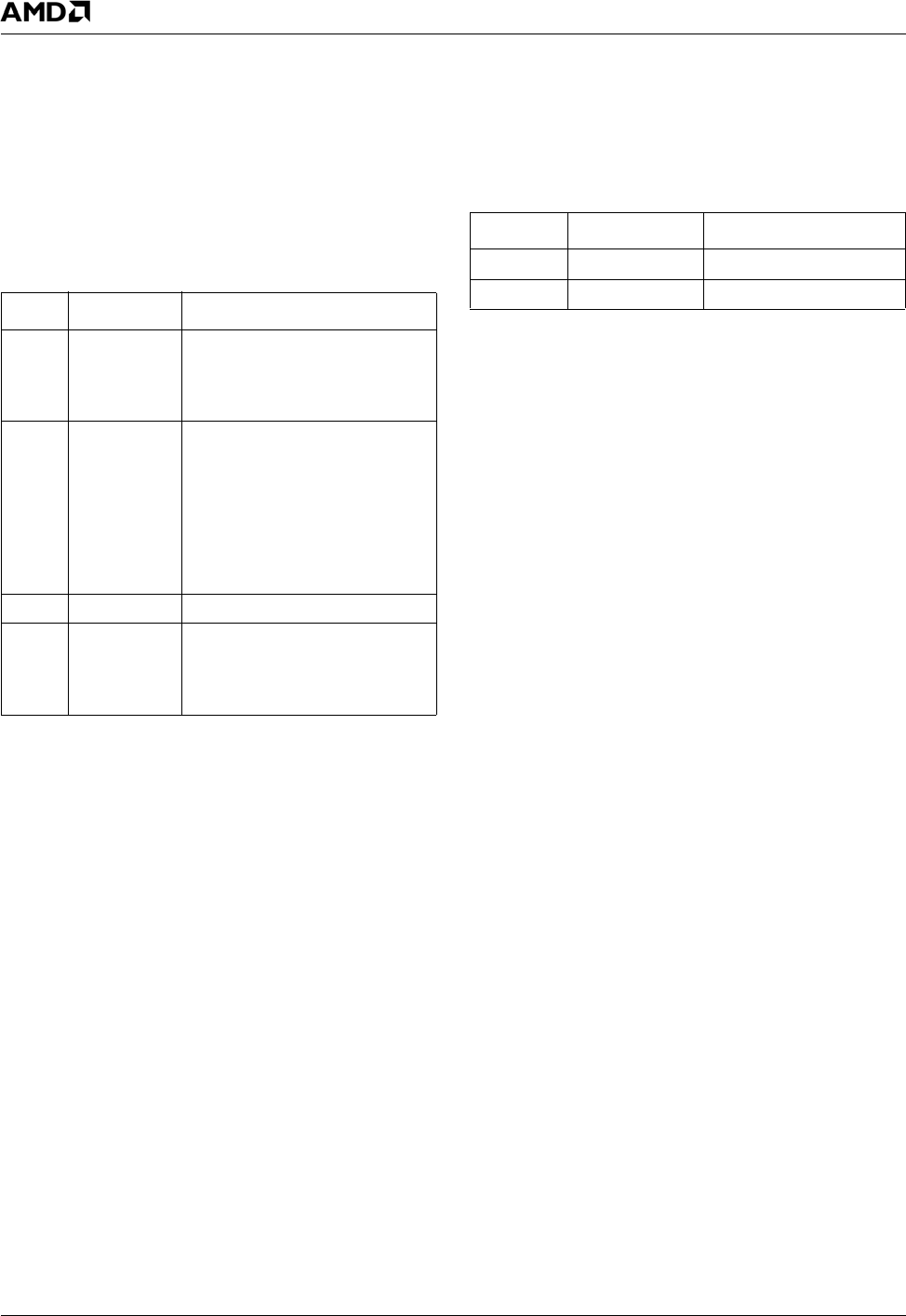

Table 6-64. SAV VIP Flags

Bit Flag Description

3

NON_INT 1 indicates that the video is from

a non-interlaced source. 0 indi-

cates that the video is from an

interlaced source.

2

REPEAT 1 indicates that the current field

is a repeat field. This occurs

during 3:2 pull-down. This flag

enables a VIP master to drop

the repeat field in the weave

mode. This bit is not supported

in the AMD Geode™ LX proces-

sor (tied to 0).

1 RSVD Reserved.

0

EXT_FLAG 0 indicates no extended flags.

This bit is not supported in the

AMD Geode LX processor (tied

to 0).

Table 6-65. VOP Clock Rate

Level Video Port Max. PIXCLK

I 8-bit 75 MHz

II 16-bit 75 MHz