AMD Geode™ LX Processors Data Book 543

GeodeLink™ Control Processor Register Descriptions

33234H

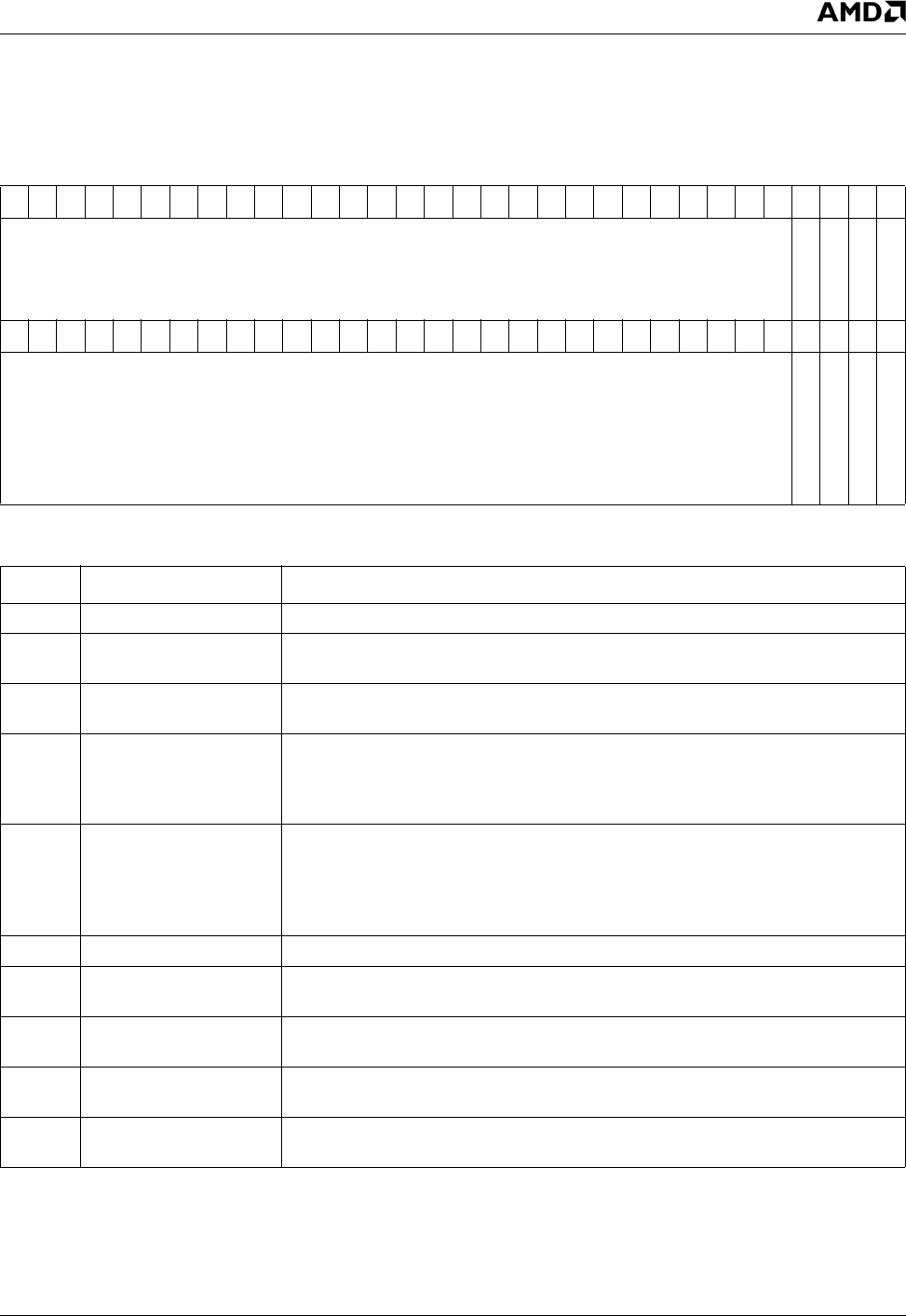

6.14.1.4 GLD Error MSR (GLD_MSR_ERROR)

MSR Address 4C002003h

Typ e R /W

Reset Value 00000000_00000000h

GLD_MSR_ERROR Register Map

63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32

RSVD

ERR_SYSPLL

ERR_DOTPLL

ERR_SIZE

ERR_TYPE

313029282726252423222120191817161514131211109876543210

RSVD

ERR_SYSPLL_MASK

ERR_DOTPLL_MASK

ERR_SIZE_MASK

ERR_TYPE_MASK

GLD_MSR_ERROR Bit Descriptions

Bit Name Description

63:36 RSVD Reserved.

35 ERR_SYSPLL Error System PLL. System PLL lock signal was active when POR was inactive.

Writing 1 clears error; 0 leaves unchanged.

34 ERR_DOTPLL Error Dot Clock PLL. Dot clock PLL lock signal was active when POR was inac-

tive. Writing 1 clears error; 0 leaves unchanged.

33 ERR_SIZE Error Size. The GLIU interface detected a read or write of more than 1 data

packet (size = 16 bytes or 32 bytes). If a response packet is expected, the excep-

tion bit will be set, in all cases the asynchronous error signal will be set. Writing 1

clears error; 0 leaves unchanged.

32 ERR_TYPE Error Type. An unexpected type was sent to the GLCP GLIU interface (start

request with BEX type, snoop, peek_write, debug_req, or NULL type). If a

response packet is expected, the exception bit will be set, in all cases the asyn-

chronous error signal will be set. Writing a 1 clears the error, writing a 0 leaves

unchanged.

31:4 RSVD Reserved.

3 ERR_SYSPLL_MASK Error System PLL Mask. When set to 1, disables error signaling based on the

state of the ERR_SYSPLL flag (bit 35).

2 ERR_DOTPLL_MASK Error Dot Clock PLL Mask. When set to 1, disables error signaling based on the

state of the ERR_DOTPLL flag (bit 34).

1 ERR_SIZE_MASK Error Size Mask. When set to 1, disables error signaling based on the state of

the ERR_SIZE flag (bit 33).

0 ERR_TYPE_MASK Error Type Mask. Wh.en set to 1, disables error signaling based on the state of

the ERR_TYPE flag (bit 32).