AMD Geode™ LX Processors Data Book 293

Display Controller

33234H

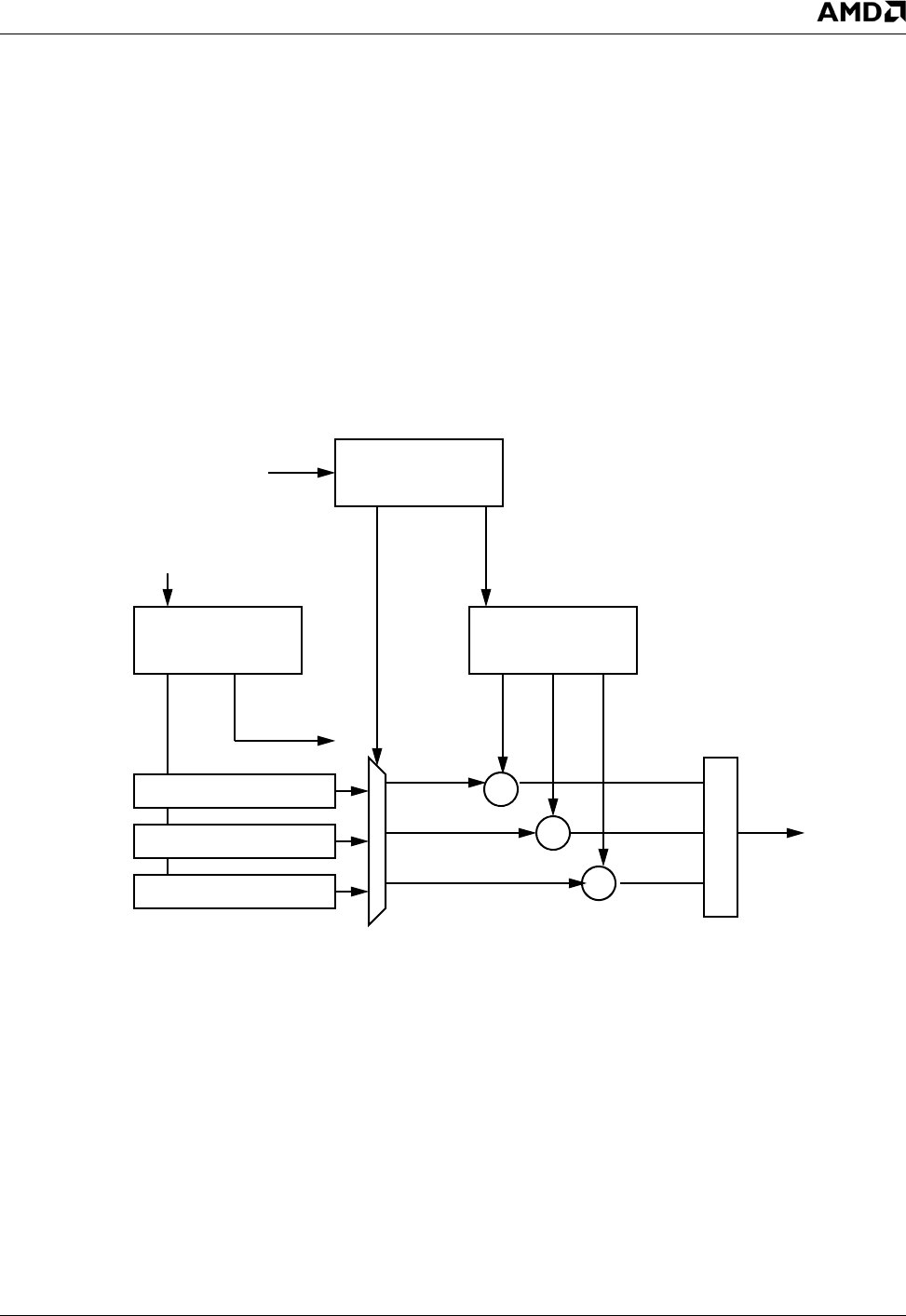

6.5.6 Graphics Scaler/Filter

The DC incorporates a 3x5 tap filter to be used for up/

downscaling of the graphics image. In order to support the

filter, three lines of buffering are also included. These three

line buffers support a frame buffer resolution of up to 1024

pixels wide. For wider images, the buffers are automatically

reconfigured into one line, and scaling is not supported. For

frame buffer images up to and including 1024 pixels in

width, vertical downscaling of up to (but not including) 2:1

is supported and horizontal downscaling of up to (but not

including) 2:1 is supported.

The filter is organized as five 3-tap vertical filters that feed

the five taps of a horizontal filter. The filter supports 1/256

inter-pixel quantization (i.e., 256-phase) in both the hori-

zontal and vertical directions. The filter coefficients are 10

bits wide.

Scaling is controlled by adjusting the horizontal and vertical

filter scale factors (through configuration register 90).

These numbers represent binary rational numbers in a

2.14 format. At the start of each frame, the H Phase Adder

and V Phase Adder are reset to 0. At the start of each scan

line, the V Phase adder is added to V Phase and the result

is stored in V Phase Adder. The integer portion of the value

in V Phase Adder indicates on which line the filter kernel is

centered. The most significant eight bits of the fractional

portion of this value determine the vertical phase for the

purpose of determining the filter coefficients.

The H Phase Adder mechanism is similar but operates on

pixels instead of lines.

A block diagram of the filter is shown in Figure 6-20.

Figure 6-20. Graphics Filter Block Diagram

V Phase Adder

H Phase Adder V. Coefficient RAM

X

X

X

+

Address

H Phase

V Phase

Line buffer selection

and routing

Address

Address for H.

Coefficient RAM

Line Buffer

Line Buffer

Line Buffer

To

horizontal

latches