628 AMD Geode™ LX Processors Data Book

Instruction Set

33234H

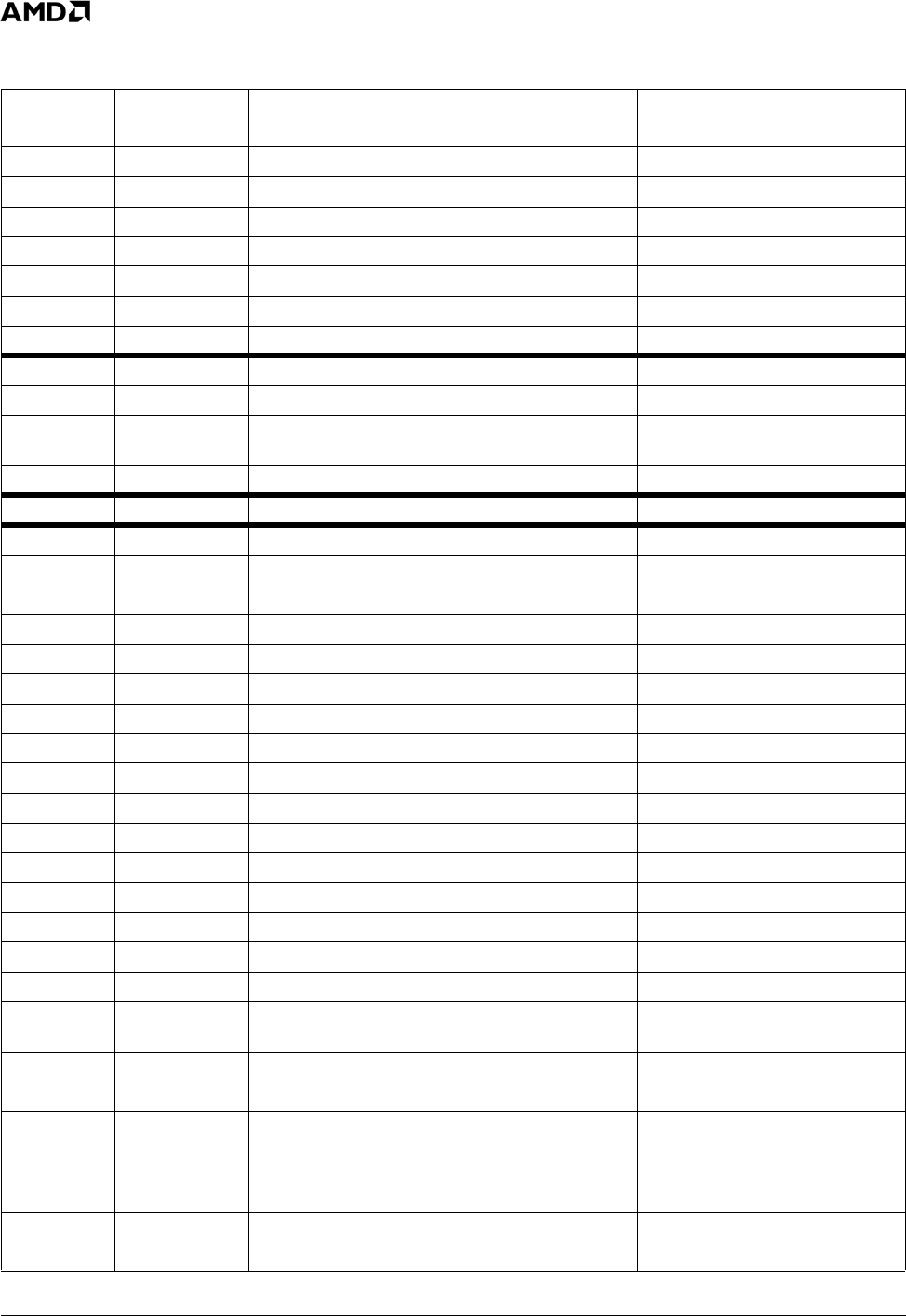

Table 8-18. CPUID Instruction Codes with EAX = 00000000

Register

Reset

Value Description Comment

EAX[31:28] 0x0 Reserved

EAX[27:20] 0x00 Extended Family

EAX[19:16] 0x00 Extended Model

EAX[15:12] 0x0 Reserved

EAX[11:8] 0x5 Processor/Instruction Family

EAX[7:4] 0xA Processor Model

EAX[3:0] 0x2 Processor Stepping May change with CPU revision

EBX[31:24] 0x00 Initial local APCI physical ID

EBX[23:16] 0x00 Reserved

EBX[15:08] 0x04 CLFLUSH cache line size in QWORD - 8 byte

increments

EBX[7:0] 0x00 8-bit brand ID

EDX[31:27] 0000 Reserved

EDX[26] 0 XMM2. Streaming SIMD Extensions Not supported

EDX[25] 0 XMM. Streaming SIMD Extensions Not supported

EDX[24] 0 FXSR. Fast FP Save and Restore Not supported

EDX[23] 1 MMX™. MMX Instruction Set and Architecture

EDX[22:20] 000 Reserved

EDX[19} 1 CLFSH. CLFLUSH feature is supported

EDX[18] 0 PN. 96-Bit Serial Number Feature Not supported

EDX[17] 0 PSE36. 36-Bit Page Size Extensions Not supported

EDX[16] 0 PAT. Page Attribute Table Not supported

EDX[15] 1 CMOV. Conditional Move Instruction

EDX[14] 0 MCA. Machine Check Architecture Not supported

EDX[13] 1 PGE. Page Global Enable Feature

EDX[12] 0 MTRR. Memory Type Range Registers Not supported

EDX[11] 1 SEP. Sysenter/Sysexit Instruction

EDX[10] 0 Reserved

EDX[9] 0 APIC. Advanced Programmable Interrupt Not supported

EDX[8] 1 CX8. Compare Exchange (CMPXCHG8B)

Instruction

EDX[7] 0 MCE. Machine Check Exception Not supported

EDX[6] 0 PAE. Page Address Extension Not supported

EDX[5] 1 MSR. Model Specific Registers via

RDMSR/WRMSR Instructions

EDX[4] 1 TSC. Time Stamp Counter and RDTSC

Instruction

EDX[3] 1 PSE. 4 MB Page Size Extension

EDX[2] 1 DE. Debugging Extension