4–20 Cache and External Interfaces

Alpha 21264/EV67 Hardware Reference Manual

System Port

4.7.3.2 Page Hit Mode

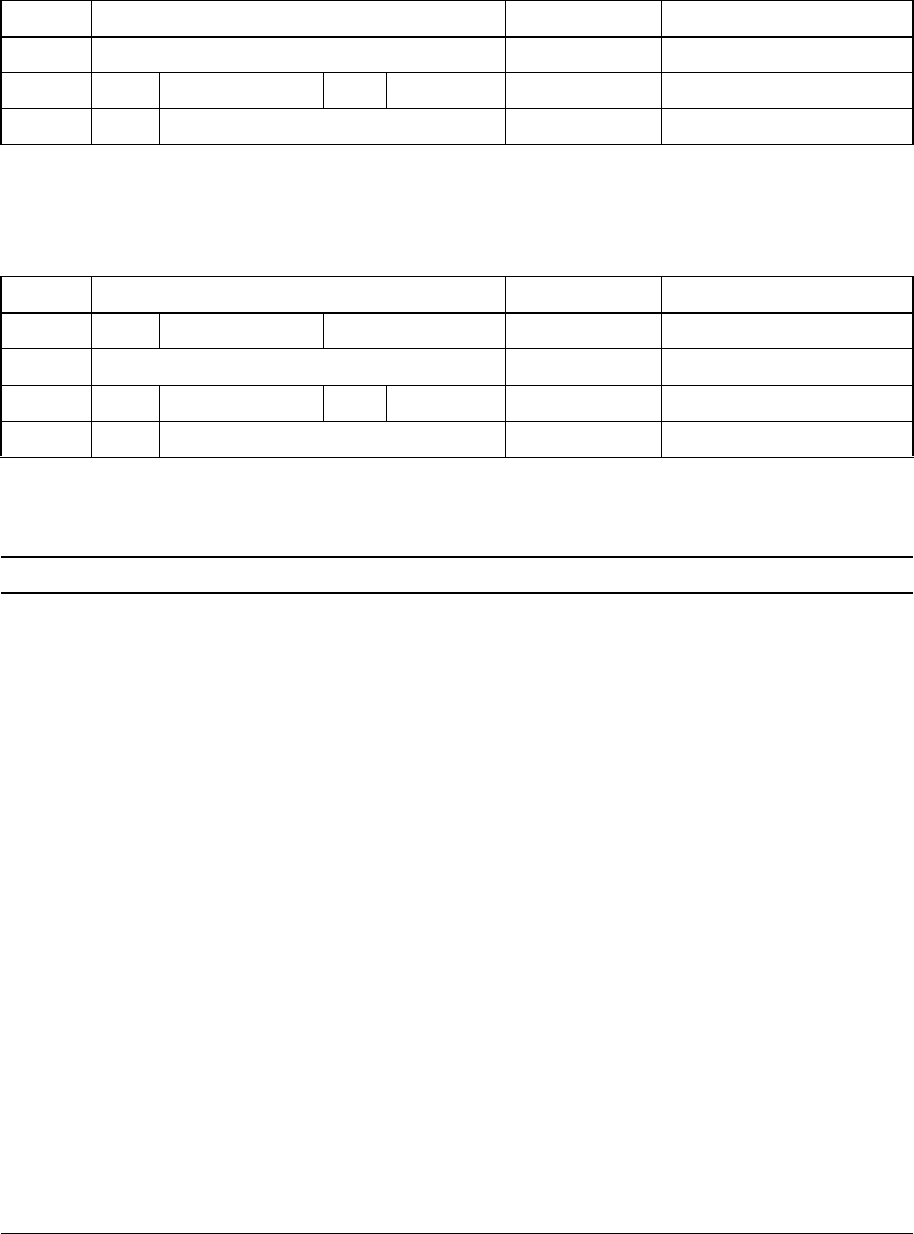

Table 4–11 shows the command format for page hit mode (21264/EV67-to-system).

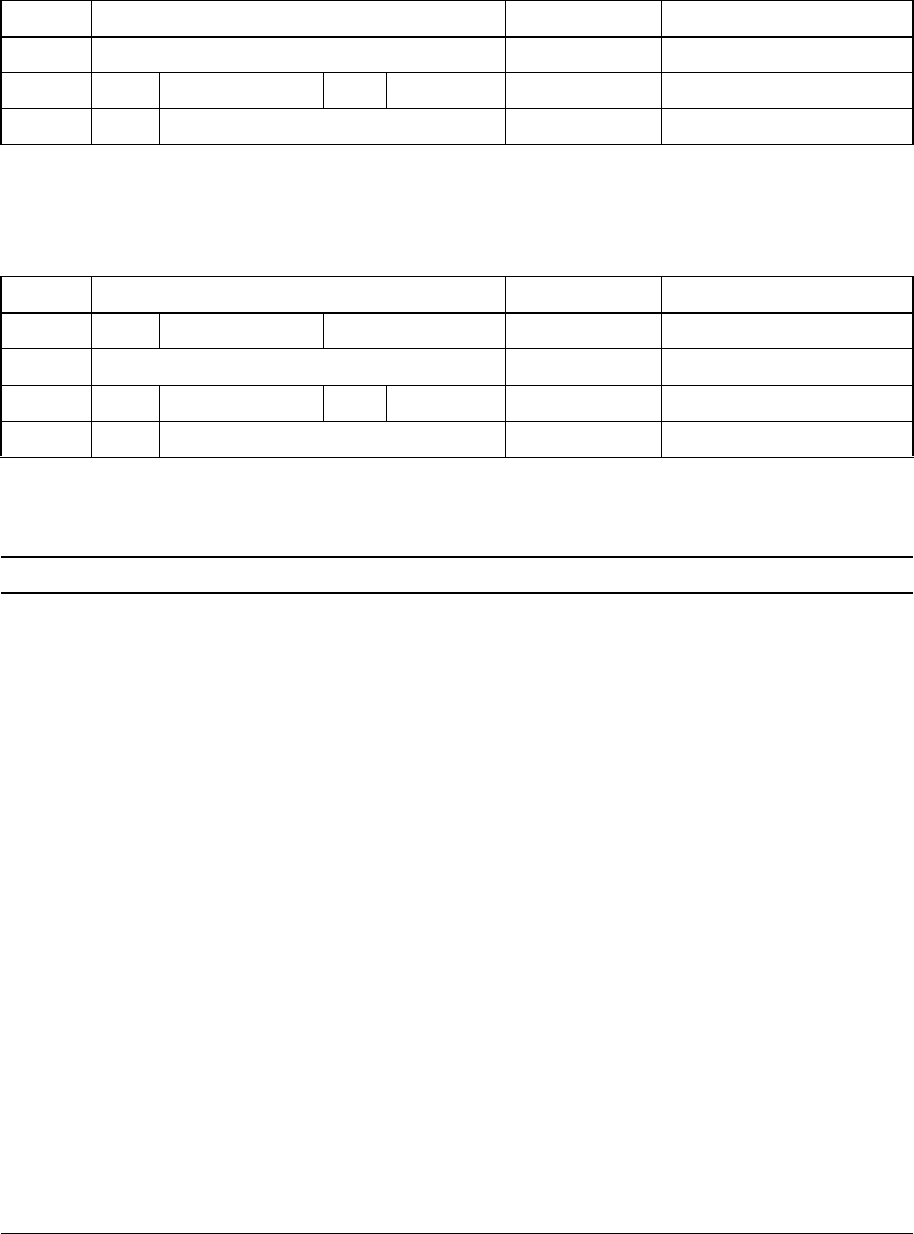

Table 4–12 describes the field definitions for Tables 4–10 and 4–11.

Cycle 2 PA[27:22], PA[12:6] PA[35] PA[37]

Cycle 3 M2 Mask[7:0] CH ID[2:0] PA[40] PA[42]

Cycle 4 RV PA[21:13], PA[5:3] PA[39] PA[41]

Table 4–11 Page Hit Mode of Operation

SysAddOut_L[14:2] SysAddOut_L[1] SysAddOut_L[0]

Cycle 1 M1 Command[4:0] PA[31:25] PA[32] PA[33]

Cycle 2 PA[24:12] PA[11] PA[34]

Cycle 3 M2 Mask[7:0] CH ID[2:0] PA[35] PA[37]

Cycle 4 RV PA[34:32], PA[11:3] PA[36] PA[38]

Table 4–12 21264/EV67-to-System Command Fields Definitions

SysAddOut Field Definition

M1 When set, reports a miss to the system for the oldest probe.

When clear, has no meaning.

Command[4:0] The 5-bit command field is defined in Table 4–14.

SysAddOut[1:0] This field is needed for systems with greater than 32GB of memory, up to a maximum of 8

Terabyte (8TB). Cost-focused systems can tie these bits high and use a 13-bit command/

address field.

M2 When set, reports that the oldest probe has missed in cache. Also, this bit is set for system-

to-21264/EV67 probe commands that hit but have no data movement (see the CH bit,

below).

When clear, has no meaning.

M1 and M2 are not asserted simultaneously. Reporting probe results as soon as possible is

critical to high-speed operation, so when a result is known the 21264/EV67 uses the earli-

est opportunity to send an M signal to the system. M bit assertion can occur either in a

valid command or a NZNOP.

ID[2:0] The ID number for the MAF, VDB, or WIOB associated with the command.

RV If set, validates this command.

In speculative read mode (optional), RV = 1 validates the command and RV = 0 indicates

a NOP.

For all nonspeculative commands RV = 1.

Mask[7:0] The byte, LW, or QW mask field for the corresponding I/O commands.

CH The cache hit bit is asserted, along with M2, when probes with no data movement hit in

the Dcache or Bcache. This response can be generated by a probe that explicitly indicates

no data movement or a ReadIfDirty command that hits on a valid but clean or shared

block.

Table 4–10 Bank Interleave on Cache Block Boundary Mode of Operation (Continued)

SysAddOut_L[14:2] SysAddOut_L[1] SysAddOut_L[0]