21264/EV68A Hardware Reference Manual

Internal Processor Registers 5–7

Ibox IPRs

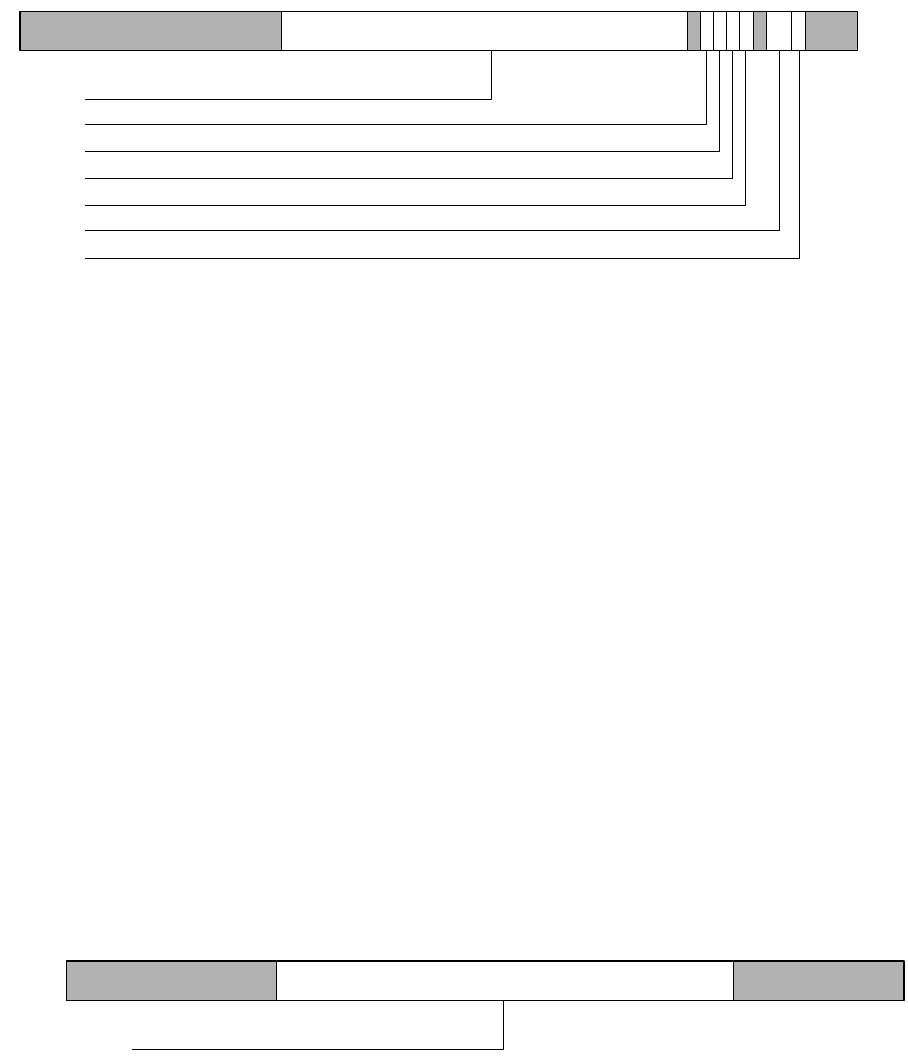

Figure 5–9 ITB PTE Array Write Register

5.2.3 ITB Invalidate All Process (ASM=0) Register – ITB_IAP

The ITB invalidate all process register (ITB_IAP) is a pseudo register that, when writ-

ten to, invalidates all ITB entries whose ASM bit is clear. An explicit write to

IC_FLUSH_ASM is required to flush the Icache of blocks with ASM equal to zero.

5.2.4 ITB Invalidate All Register – ITB_IA

The ITB invalidate all register (ITB_IA) is a pseudo register that, when written to,

invalidates all ITB entries. An explicit write to IC_FLUSH is required to flush the

Icache.

5.2.5 ITB Invalidate Single Register – ITB_IS

The ITB invalidate single register (ITB_IS) is a write-only register. Writing a virtual

page number to this register invalidates any ITB entry that meets one of the following

criteria:

• The ITB entry’s virtual page number matches ITB_IS[47:13] (or fewer bits if gran-

ularity hint bits are set in the ITB entry) and its ASN field matches the address

space number supplied in PCTX[46:39].

• The ITB entry’s virtual page number matches ITB_IS[47:13] and its ASM bit is set.

Figure 5–10 shows the ITB invalidate single register.

Figure 5–10 ITB Invalidate Single Register

Note:

Because the Icache is virtually indexed and tagged, it is normally not nec-

essary to flush the Icache when paging. Therefore, a write to ITB_IS will

not flush the Icache.

63 9876544 443 13 3121110 0

PFN[43:13]

URE

SRE

ERE

KRE

GH[1:0]

ASM

LK

99

-

00

1

6

A

63 4847 1312 0

INVAL_ITB[47:13]

LK99-0017A