11–6 Testability and Diagnostics

21264/EV68A Hardware Reference Manual

Power-Up Self-Test and Initialization

In the SROM represented in Figure 11–3, the length for fields Cbox Config

Data(0,n) plus MBZ(m,0) must equal 367 bits. (If Cbox Config Data(0,n) is

(0,366), MBZ would be zero.)

For the 21264/EV68A, Cbox Config Data is 304 bits; the value for n is 303.

Therefore, the value MBZ field for Pass 3 is:

MBZ(m,0) = 367 minus 304 = 63 = (62,0)

Tables 11–4 and 5–24 describe the details of the Icache and Cbox bit fields, respec-

tively. Note that fetch_count(1,0) must be 3, which guarantees that the SROM never

partially loads an Icache block.

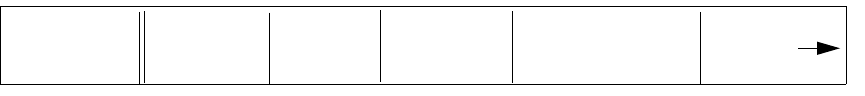

Figure 11–3 SROM Content Map

11.5.2.1 Serial Instruction Cache Load Operation

All Icache bits, including each block’s tag, address space number (ASN), address space

match (ASM), and valid and branch history bits are loaded serially from offchip serial

ROMs. Once the serial load has been invoked by the chip reset sequence, the cache is

loaded from the lower to the higher addresses.

The serial Icache fill invoked by the chip reset sequence operates internally at a fre-

quency of .

Table 11–4 lists the Icache bit fields in an SROM line. Fetch bits are listed in the order

of shift direction (to down and to right). In Table 11–4:

The load occurs at the rate of 1 bit per 256 CPU cycles. The chip outputs a 50% duty

cycle clock on the SromClk_H pin.

The serial ROMs can contain enough Alpha code to complete the configuration of the

external interface (for example, set the timing on the external cache RAMs, and diag-

nose the path between the CPU chip and the real ROM).

Bit Type Meaning

c Disp_add carry

i Instruction

iq Iqueue predecodes

tr Trouble bits

dv Destination valid

ea Ea_src

par-MBZ Must be zero

fetch [0](0,192) fetch[j-1](0,192) fetch[j](0,192) fetch_count(11,0) Cbox Config Data(0, n) MBZ(m,0)

(first block) (last block)

GCLK

256

-------- --------