21264/EV68A Hardware Reference Manual

Internal Processor Registers 5–5

Ebox IPRs

Table 5–3 describes the virtual address control register fields.

5.1.5 Virtual Address Format Register – VA_FORM

The virtual address format register (VA_FORM) is a read-only register. It contains the

virtual page table entry address derived from the faulting virtual address stored in the

VA register. It also contains the virtual page table base and associated control bits stored

in the VA_CTL register.

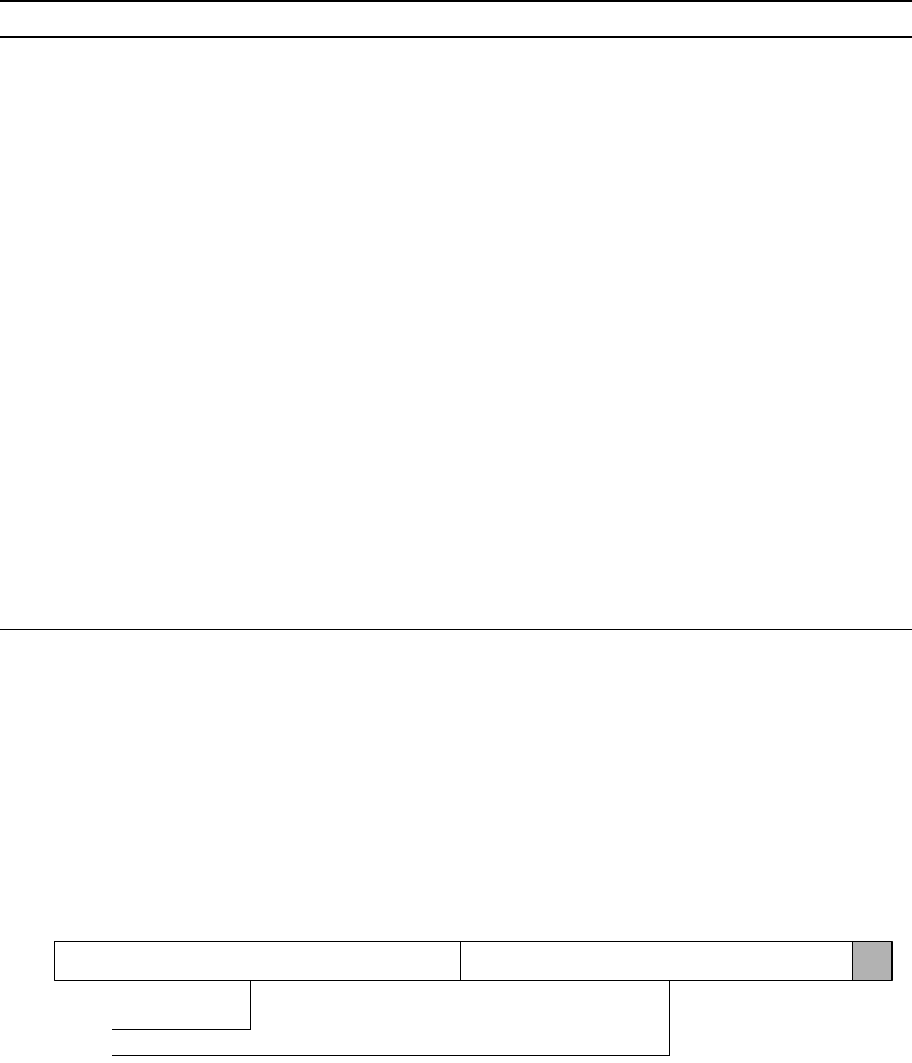

Figure 5–5 shows VA_FORM when VA_CTL(VA_48) equals 0 and

VA_CTL(VA_FORM_32) equals 0.

Figure 5–5 Virtual Address Format Register (VA_48 = 0, VA_FORM_32 = 0)

Figure 5–6 shows VA_FORM when VA_CTL(VA_48) equals 1 and

VA_CTL(VA_FORM_32) equals 0.

Table 5–3 Virtual Address Control Register Fields Description

Name Extent Type Description

VPTB[63:30] [63:30] WO Virtual Page Table Base.

See the VA_FORM register section for details.

Reserved [29:3] — —

VA_FORM_32 [2] WO This bit is used to control address formatting when reading the

VA_FORM register. See the section on the VA_FORM register for

details.

VA_48 [1] WO,0 This bit controls the format applied to effective virtual addresses

by the VA_FORM register and the memory pipe virtual address

sign extension checkers. When VA_48 is clear, the 43-bit virtual

address format is used, and when VA_48 is set, the 48-bit virtual

address format is used.

When VA_48 is set, the sign extension checkers generate an

access control violation (ACV) if VA[63:0] ≠ SEXT (VA[47:0]).

When VA_48 is clear, the sign extension checkers generate an

ACV if VA[63:0] ≠ SEXT(VA[42:0]).

B_ENDIAN [0] WO Big Endian Mode.

When set, the shift amount (Rbv[2:0]) is inverted for EXTxx,

INSxx, and MSKxx instructions. The lower bits of the physical

address for Dstream accesses are inverted based upon the length

of the reference as follows:

Byte: Invert bits [2:0]

Word: Invert bits [2:1]

Longword: Inverts bit [2]

VPTB[63:33]

VA[42:13]

63 33 332 20

LK99-0011A