21264/EV68A Hardware Reference Manual

Internal Processor Registers 5–15

Ibox IPRs

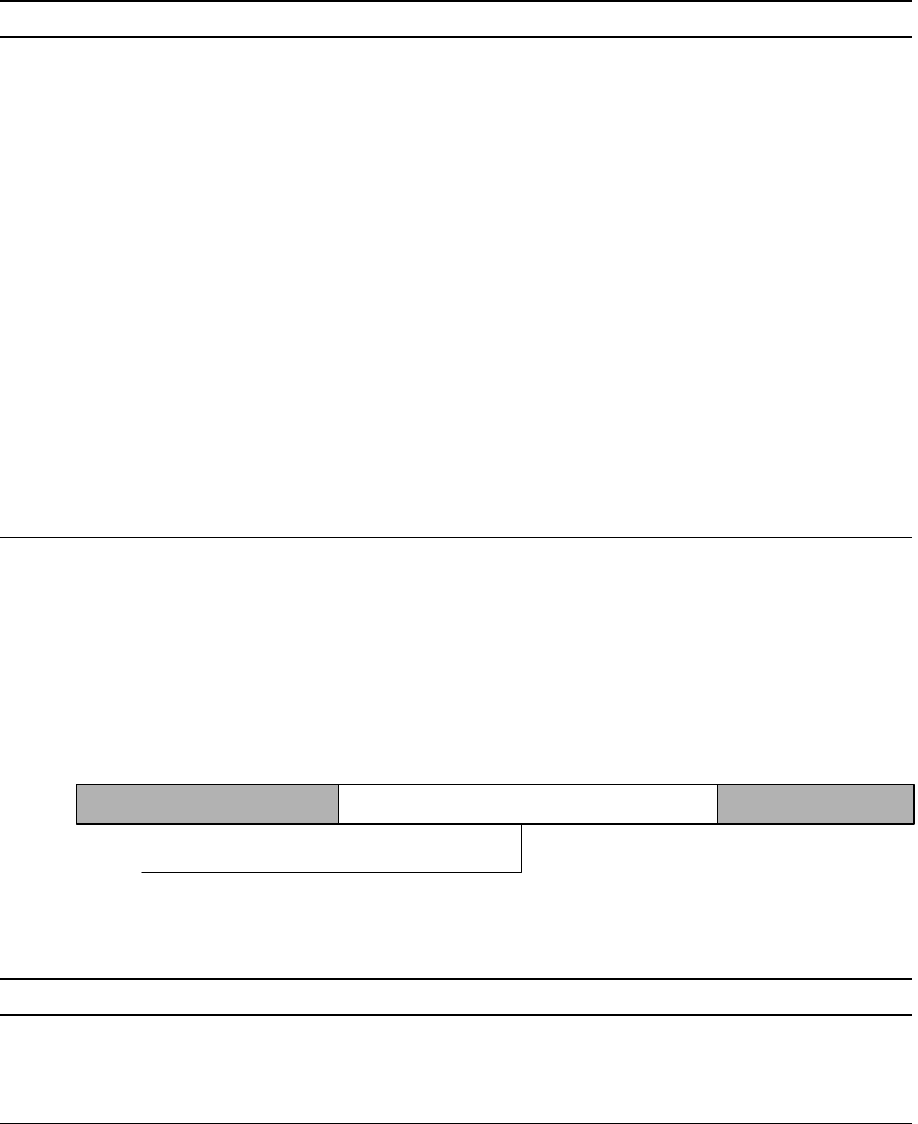

5.2.14 PAL Base Register – PAL_BASE

The PAL base register (PAL_BASE) is a read-write register that contains the base phys-

ical address for PALcode. Its contents are cleared by chip reset but are not cleared after

waking up from sleep mode or from fault reset. Figure 5–21 shows the PAL base regis-

ter.

Figure 5–21 PAL Base Register

Table 5–10 describes the PAL base register fields.

5.2.15 Ibox Control Register – I_CTL

The Ibox control register (I_CTL) is a read-write register that controls various Ibox

functions. Its contents are cleared by chip reset. Figure 5–22 shows the Ibox control

register.

REG[4:0] [12:8] RO Destination register of load or operate instruction that triggered

the trap OR source register of store that triggered the trap. These

bits may contain the Rc field of an operate instruction or the Ra

field of a load or store instruction. The value is UNPREDICTABLE

ifthetrapwastriggeredbyanITBmiss,interrupt,OPCDEC,or

other non load/st/operate.

INT [7] RO Set to indicate Ebox integer overflow trap, clear to indicate Fbox

trap condition.

IOV [6] RO Indicates Fbox convert-to-integer overflow or Ebox integer over-

flow trap.

INE [5] RO Indicates floating-point inexact error trap.

UNF [4] RO Indicates floating-point underflow trap.

FOV [3] RO Indicates floating-point overflow trap.

DZE [2] RO Indicates divide by zero trap.

INV [1] RO Indicates invalid operation trap.

SWC [0] RO Indicates software completion possible. This bit is set if the

instruction that triggered the trap contained the /S modifier.

Table 5–10 PAL Base Register Fields Description

Name Extent Type Description

Reserved [63:44] RO, 0 Reserved for COMPAQ.

PAL_BASE[43:15] [43:15] RW Base physical address for PALcode.

Reserved [14:0] RO, 0 Reserved for COMPAQ.

Table 5–9 Exception Summary Register Fields Description (Continued)

Name Extent Type Description

63 1544 1443 0

PAL_BASE[43:15]

LK99-0027A